# Fuji IGBT Module

# **Application Manual**

## **A** Cautions

This manual contains the product specifications, characteristics, data, materials, and structures as of March 2023.

The contents are subject to change without notice for specification changes or other reasons. When using a product listed in this manual, be sure to obtain the latest specifications.

Fuji Electric Co., Ltd. is constantly making every endeavor to improve the product quality and reliability. However, on rare occasions, semiconductor products may fail or malfunction. To prevent accidents causing injury or death, damage to property like by fire, and other social damage resulted from a failure or malfunction of the Fuji Electric Co., Ltd. semiconductor products, take measures to ensure safety such as redundant design, fire spread prevention design, and malfunction prevention design.

The contents described in this specification never ensure to enforce the industrial property and other rights, nor license the enforcement rights.

The products described in this specification are not designed nor made for being applied to the equipment or systems used under life-threatening situations. When you consider applying the product of this specification to particular use, such as vehicle-mounted units, shipboard equipment, aerospace equipment, medical devices, atomic control systems and submarine relaying equipment or systems, Fuji Electric is not responsible for the applicability.

The data and other information contained in this specification are guaranteed for the product, but do not guaranteed the characteristics and quality of the equipment applying this product. When using this product, please evaluate it in the application in which it will be used, and then judge its applicability at user's own risk. Fuji Electric is not responsible for the applicability.

## Contents

| Chapter 1 Structure and Features                         | 1-1        |

|----------------------------------------------------------|------------|

| History of IGBT Structure                                | 1-2        |

| 2. Module structure                                      | 1-4        |

| Circuit Configuration of IGBT Module                     | 1-5        |

| Overcurrent Limiting Feature                             | 1-6        |

| 5. RoHS Compliance                                       | 1-6        |

| 6. Standards for Safety: UL Certification                | 1-6        |

| Observan O. Tarres and Observatoristics                  | 0.4        |

| Chapter 2 Terms and Characteristics                      | 2-1<br>2-2 |

| Explanation of Terms     Characteristics of IGBT and FWD |            |

| 2. Characteristics of IGBT and FWD                       | 2-5        |

|                                                          |            |

| Chapter 3 IGBT Module Selection and Application          | 3-1        |

| Selection of IGBT Module Ratings                         | 3-2        |

| 2. Static Electricity Countermeasures                    | 3-4        |

| Protection Circuits Design                               | 3-5        |

| 4. Cooling Design                                        | 3-5        |

| 5. Gate Drive Circuits Design                            | 3-5        |

| 6. Parallel Connection                                   | 3-6        |

| 7. Mounting Notes                                        | 3-6        |

| 8. Storage and Transportation Notes                      | 3-8        |

| 9. Reliability Notes (Lifetime Design)                   | 3-9        |

| 10. Other Precautions                                    | 3-10       |

|                                                          |            |

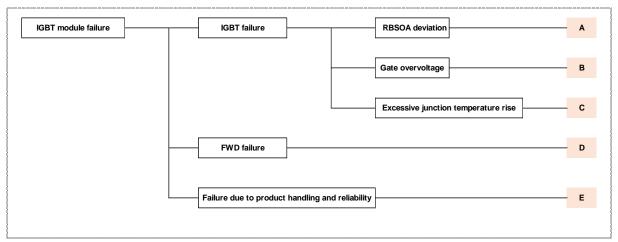

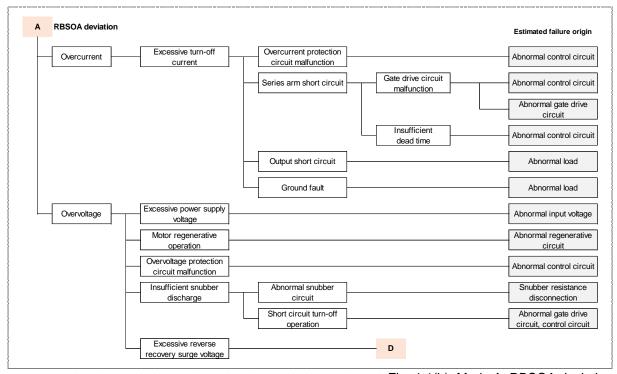

| Chapter 4 Typical Troubles and Troubleshooting           | 4-1        |

| 1. Troubleshooting                                       | 4-2        |

| 2. IGBT Test Procedures                                  | 4-7        |

| Typical Troubles and Troubleshooting                     | 4-8        |

| Chapter 5 Protection Circuit Design                                      | 5-1  |

|--------------------------------------------------------------------------|------|

| Short Circuit (Overcurrent) Protection                                   | 5-2  |

| 2. Overvoltage Protection                                                | 5-8  |

|                                                                          |      |

| Chapter 6 Cooling Design                                                 | 6-1  |

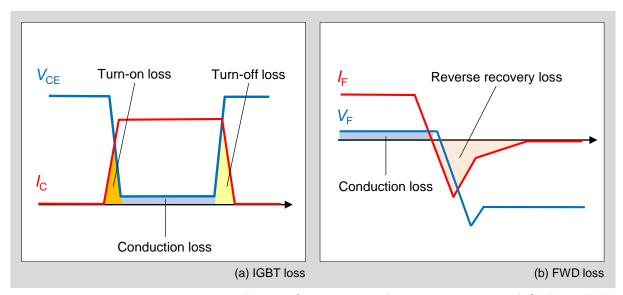

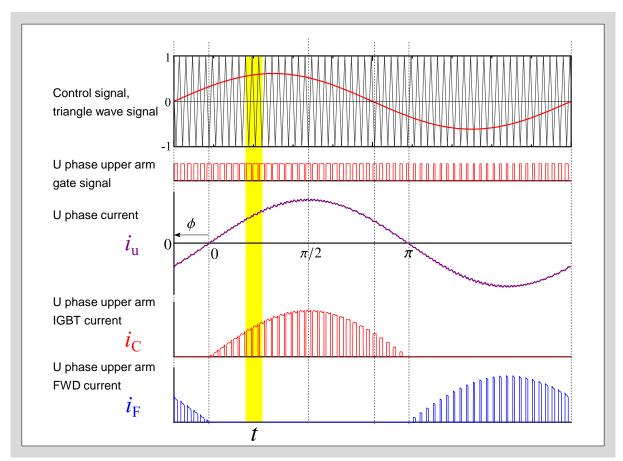

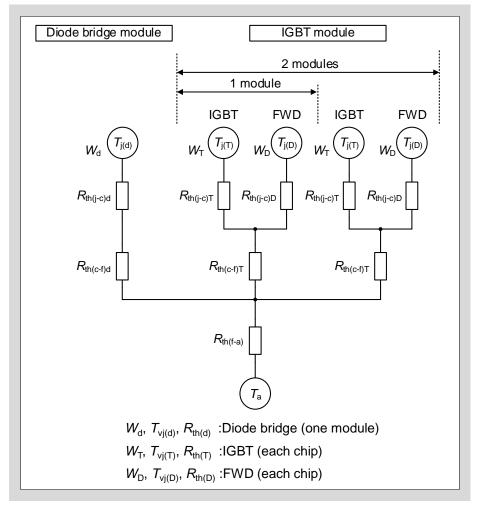

| Power Loss of IGBT Module                                                | 6-2  |

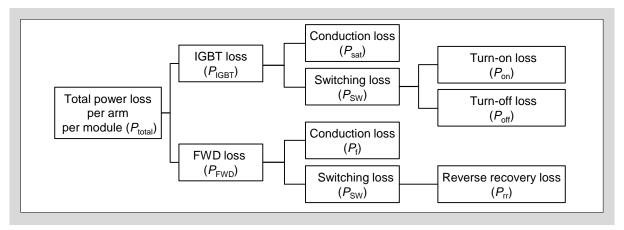

| Power Loss Calculation Method of Boost Chopper Circuit                   | 6-3  |

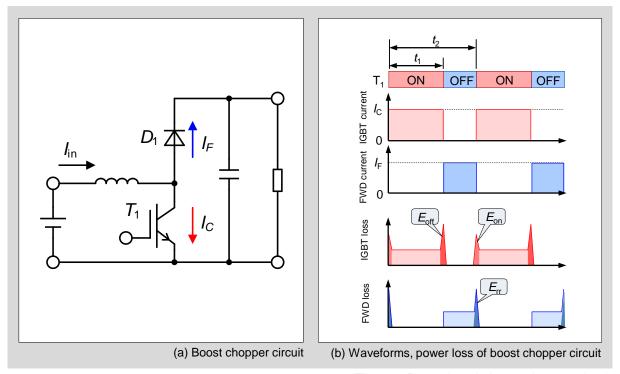

| 3. Power Loss Calculation Method of 3-phase 2-level PWM Inverter Circuit | 6-4  |

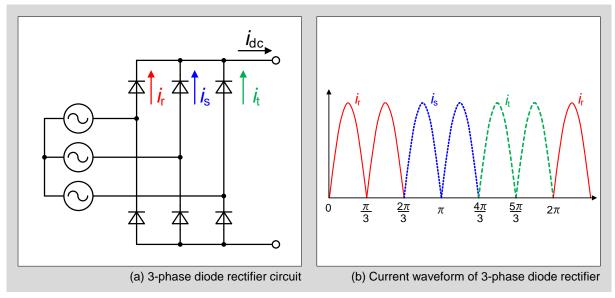

| 4. Power Loss Calculation Method of 3-phase Diode Rectifier Circuit      | 6-8  |

| 5. Selecting Heatsink                                                    | 6-9  |

| 6. Mounting Precautions                                                  | 6-12 |

| Chapter 7 Gate Drive Circuit Design                                      | 7-1  |

| IGBT Gate Drive Conditions and Main Characteristics                      | 7-2  |

| 2. Drive Current                                                         | 7-5  |

| 3. Setting Dead Time                                                     | 7-6  |

| 4. Examples of Gate Drive Circuits                                       | 7-8  |

| 5. Precautions for Gate Drive Circuit Design                             | 7-9  |

| Chapter 8 Parallel Connections                                           | 8-1  |

| 1. Selection of IGBT Modules                                             | 8-2  |

| 2. Main Circuit Design                                                   | 8-6  |

| 3. Gate Drive Circuit Design                                             | 8-9  |

| 4. Cooling Design                                                        | 8-12 |

| Chapter 9  | Evaluation and Measurement                           | 9-1   |

|------------|------------------------------------------------------|-------|

| 1. Applica | ation Scope                                          | 9-2   |

| 2. Evalua  | tion and Measurement methods                         | 9-2   |

| Chapter 1  | 0 EMC Design of IGBT Module                          | 10-1  |

| 1. Genera  | al Information of EMC in Power Electronics Equipment | 10-2  |

| 2. EMI Co  | ountermeasure Design for Inverters                   | 10-4  |

| 3. EMI Co  | ountermeasures in IGBT Modules Application           | 10-11 |

| Chapter 1  | 1 Reliability of Power Modules                       | 11-2  |

| 1. Basis o | of Reliability                                       | 11-2  |

| 2. Reliabi | ility Test Conditions                                | 11-4  |

| 3. Power   | Cycling Lifetime                                     | 11-5  |

## Chapter 1 Structure and Features

| History of IGBT Structure                 | 1-2 |

|-------------------------------------------|-----|

| 2. Module Structure                       | 1-4 |

| 3. Circuit Configuration of IGBT Module   | 1-5 |

| Overcurrent Limiting Feature              | 1-6 |

| 5. RoHS Compliance                        | 1-6 |

| 6. Standards for Safety: UL Certification | 1-6 |

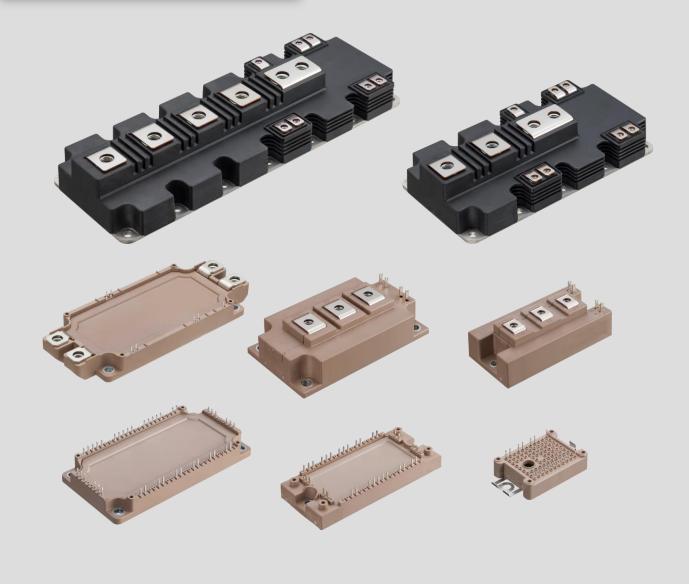

The insulated gate bipolar transistors (IGBTs), applied to equipment such as variable-speed motor drives and uninterruptible power supplies for computers, are developing rapidly in response to the increasing demand for energy saving, weight reduction, and downsizing of equipment in recent years. The IGBT is a switching device designed to have the high-speed switching performance and gate voltage control of a power MOSFET as well as the high-voltage / large-current handling capability of bipolar transistor.

## 1. History of IGBT Structure

The n-channel IGBT, which forms a n-type inversion layer when positive voltage is applied to the gate, has a structure in which the n+ layer on the drain side of the power MOSFET is replaced with a p+ layer. It is a bipolar device that can reduce on-resistance at large current with conductivity modulation.

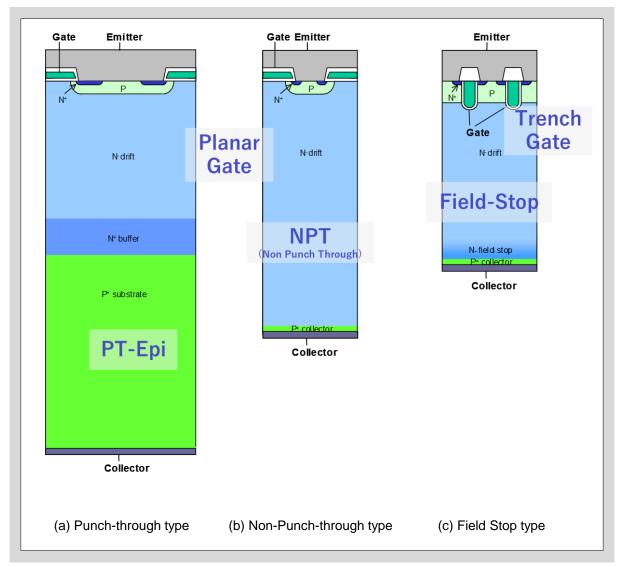

The IGBT structure can be roughly divided into the surface gate structure, the bulk structure that forms the n-drift layer, and the backside structure. There are two types of surface gate structures. One is the planar gate structure, in which the gates are formed on the wafer surface, namely the chip surface. The other is the trench gate structure, in which trenches are made to form the gates in the wafer. On the other hand, the bulk structure can be roughly divided into the punch-through type, in which the depletion layer reaches the collector side at turn-off, and the non-punch-through type, in which it does not reach the collector side. The comparison of the n-channel IGBTs is shown in Fig. 1-1.

Fuji Electric has been supplying IGBTs to the market since it commercialized them in 1988. The planar-gate punch-through IGBT was the mainstream IGBT at that time. The punch-through IGBT used the epitaxial wafer and low on-state voltage was achieved by injecting a large amount of minority carriers from the collector layer to obtain conductivity modulation effect. At the same time, the lifetime control technology was used because the excess carriers, which were high-injected into the n-base layer, has to be removed quickly at turn-off. As a result, both low on-state voltage and low turn-off switching loss ( $E_{\rm off}$ ) were achieved. The lifetime control technology was widely used because it was relatively easy to apply into the IGBT manufacturing process. However, there were problems such as large variations in on-state voltage and the output characteristics showing negative temperature characteristics. Therefore, with the increasing capacity of IGBT modules and the power converters using them, the demand for IGBT characteristics that facilitate parallel connection has increased.

The non-punch-through IGBT was developed to overcome these issues. The non-punch-through IGBT controls the minority carrier injection efficiency by controlling the concentration of impurities in the collector (p-collector layer), and controls the internal electric field and transport efficiency by controlling the thickness and resistivity of the n-drift layer. The non-punch-through IGBTs use the FZ (Floating Zone) wafer instead of the epitaxial wafer. Therefore, the superiority of the FZ wafer compared to the epitaxial wafer can be reflected in the IGBT chip. For example, FZ wafers have less crystal defects and low internal stress, making it easy to manufacture high voltage chips of 1700V and above. In addition, the carrier lifetime of FZ wafers is very long, and the excess carrier distribution control of the IGBT chip only needs to consider minority carrier injection from the p-collector layer. Furthermore, variations in characteristics such as on-state voltage are greatly reduced.

On the other hand, in order to achieve a low on-state voltage, it was necessary to improve the transport efficiency. In particular, IGBT wafers with a withstand voltage of 1200V or less required a special manufacturing technology to thin the n-drift layer. Therefore, Fuji Electric has developed new technologies for production of thinner wafers and improved the characteristics.

To further improve the characteristics, IGBTs with thinner chip thickness are required. However, the thickness of the n-drift layer constitutes most of the chip thickness, and if the thickness is too thin, the specified voltage cannot be maintained. The FS (Field Stop) structure solved this problem that hinder the improvement of the characteristics. In the FS structure, a high concentration FS layer is provided in the n-drift layer. This structure makes it possible to further reduce the thickness of the chip and improve its characteristics.

Fuji Electric has also advanced the miniaturization of the surface structure that is imperative to improve the characteristics of IGBT. The IGBT is formed by arranging many basic structures called cells. The higher the number of IGBT cells, the lower the on-state voltage will be. In order to increase cell density, the surface structure has changed from the planar structure, in which the IGBT cells are formed on the wafer surface two-dimensionally, to the trench structure, in which the trenches are formed on the wafer surface and the gates structure are formed three-dimensionally. In this way, Fuji Electric has improved the characteristics by applying various technologies to the bulk structure and the surface structure.

Fig. 1-1 Structure comparison of IGBT

## 2. Module Structure

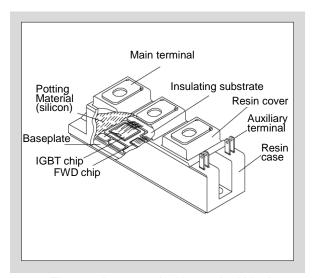

Fig. 1-2 and Fig. 1-3 show typical IGBT module structures. The module integrated with terminal block shown in Fig. 1-2 has a case and external electrode terminals molded into a single unit to reduce the number of parts required and the internal wiring inductance. In addition, the use of DCB (direct copper bonding) substrate realizes a high-reliability product that combines low thermal resistance and high bending strength.

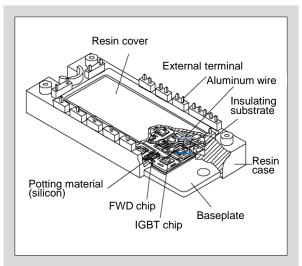

The wire terminal connection structure module shown in Fig. 1-3 has main terminals bonded to the DCB substrate by wire. As a result, the package structure has been simplified, made smaller, thinner, lighter, and reduced in assembly time.

Other design considerations implemented include optimal IGBT and FWD chips layout to assure efficient heat distribution, and the equal arrangement of IGBT chips in the upper and lower arms to balance the turn-on transient current and thus prevent the increases in turn-on loss.

Fig. 1-2 Integrated with terminal block type

Fig. 1-3 Wire terminal connection structure type

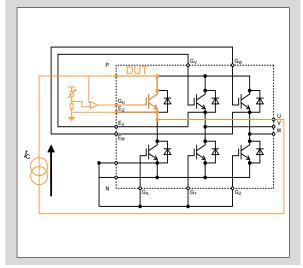

## 3. Circuit Configuration of IGBT Module

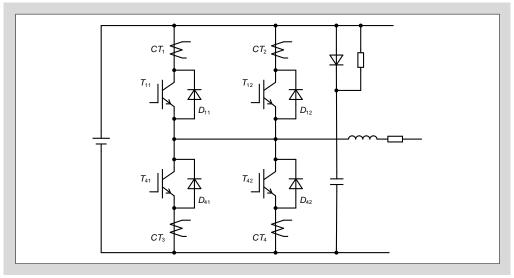

Table 1-1 shows typical circuit configuration of IGBT modules. As shown in Table 1-1, there are basically four types of IGBT modules: 1-Pack, 2-Pack, 6-Pack, and PIM. Each type has its own features. The circuit configuration is also shown. Use them as reference when selecting a module.

Table 1-1 Circuit configuration of IGBT modules

|         | Example of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Factoria                                |                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type    | External view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Equivalent circuit                      | Feature                                                                                                                                                                                                                       |

| 1-Pack  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C O E G E                               | Module which contains one IGBT and one anti-parallel FWD. Modules with high current rating are often connected in parallel in large capacity applications.                                                                    |

| Chopper |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C1 O                                    | Module which a FWD is connected in series to an IGBT and its anti-parallel FWD. For application in brake for PWM inverter. I-type 3-level circuit can be configured by combining with 2-Pack.                                 |

| 2-Pack  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C1 O E2  G1 E1 G2 E2                    | Module which contains two sets of IGBT and its anti-parallel FWD. Generally 3 modules are used to configure a PWM inverter. Products with high current rating are often connected in parallel in large capacity applications. |

| 3 Level |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 715 715 715 715 715 715 715 715 715 715 | Module consisting of IGBTs and FWDs arranged in T-type or I-type. It is generally used for solar inverters. Also, modules are often connected in parallel in large capacity applications.                                     |

| 6-Pack  | GREGE STE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | Each module contains six sets of IGBT and its anti-parallel FWD. Module with built-in NTC thermistor for temperature detection is also available. It is common to configure a PWM inverter with a single module.              |

| PIM     | Mandiandonddonnodd Control of the Control of |                                         | A module with built-in converter, inverter, and brake. Module with built-in NTC thermistor for temperature detection is also available.                                                                                       |

## 4. Overcurrent Limiting Feature

During operation, a load short circuit or similar problem may cause overcurrent in the IGBT. If the overcurrent is allowed to continue, the device may quickly overheat and be destroyed. Generally, the time span from the beginning of the overcurrent to the destruction of the device is called the "short circuit withstand capability". In addition, short circuit withstand capability becomes higher (longer) in condition with lower short circuit current and/or lower power supply voltage. In other words, the smaller the short circuit energy, the higher the short circuit withstand capability.

The short circuit current is dependent on the gate voltage. The IGBT is designed to limit the short circuit current to several times of the device current rating. Thus, in the event of a short circuit, the overcurrent is limited, allowing protection to be applied with a margin after overcurrent is detected.

### 5. RoHS Compliance

The RoHS (Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) was enacted by the EU (European Union) on July 1, 2006 to restrict the use of certain hazardous substances in electrical and electronic equipment.

The use of the following ten substances are restricted: Pb (lead), Cd (cadmium), Cr6+ (hexavalent chromium), Hg (mercury), PBB (polybrominated biphenyl), PBDE (polybrominated diphenyl ether), DEHP (bis (2-ethylhexyl) phthalate), BBP (butyl benzyl phthalate), DBP (dibutyl phthalate) and DIBP (diisobutyl phthalate).

Products containing these 10 substances above the threshold (0.01% for Cd, 0.1% for others) cannot be sold in the EU.Exemptions are allowed for uses that are technically difficult to replace.

Lead (Pb) contained in the solder used to connect each chip and DCB is particularly relevant to the RoHS compliance of IGBT modules. Fuji Electric uses Pb-free solder to commercialize products that comply with RoHS regulations.

## 6. Standards for Safety: UL Certification

When using various devices in the market in regions that require compliance with UL safety regulations such as North America, UL certification is required for the parts used in those devices.

Fuji Electric IGBT modules comply with UL1557 and are certified. The approved models can be checked in the following website.

https://productiq.ulprospector.com/en/profile/1972723/qqqx2.e82988?term=E82988&page=1

A list of Fuji Electric products which is currently UL certified is displayed.

## Chapter 2 Terms and Characteristics

| 1. | Explanation of Terms            | 2-2 |

|----|---------------------------------|-----|

| 2. | Characteristics of IGBT and FWD | 2-5 |

This chapter describes the terms and characteristics of IGBT modules.

## 1. Explanation of Terms

Various terms used in the specifications are explained below.

Table 2-1 Maximum ratings

| Term                                   | Symbol                                                                                | Definition explanation (Refer to specifications for test conditions)                                                                                                          |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

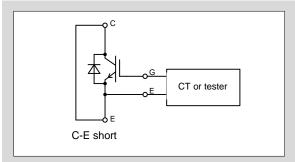

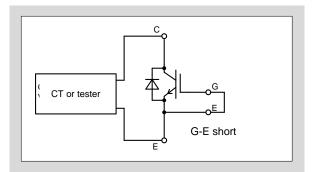

| Collector-Emitter voltage              | V <sub>CES</sub>                                                                      | Maximum Collector-Emitter (hereinafter referred to as C-E) voltage with Gate-Emitter (G-E) shorted.                                                                           |  |  |

| Gate-Emitter voltage                   | V <sub>GES</sub>                                                                      | Maximum G-E voltage with C-E shorted.                                                                                                                                         |  |  |

| Callantar accuracy                     | I <sub>C</sub>                                                                        | Maximum DC collector current of IGBT.                                                                                                                                         |  |  |

| Collector current                      | $I_{CRM}$<br>$I_{C}$ pulse                                                            | Maximum pulse collector current of IGBT.                                                                                                                                      |  |  |

| F                                      | -1 <sub>C</sub>                                                                       | Maximum DC forward current of FWD.                                                                                                                                            |  |  |

| Forward current                        | I <sub>FRM</sub> -I <sub>C</sub> pulse                                                | Maximum pulse forward current of FWD.                                                                                                                                         |  |  |

| Total power dissipation                | P <sub>tot</sub><br>P <sub>C</sub>                                                    | Maximum power dissipation per IGBT.                                                                                                                                           |  |  |

| Virtual junction temperature           | junction $T_{vj}$ Maximum junction temperature at which normal operation is positive. |                                                                                                                                                                               |  |  |

| Operating virtual junction temperature | $T_{\text{vj(op)}}$ $T_{\text{vjop}}$                                                 | Junction temperature during continuous operation.                                                                                                                             |  |  |

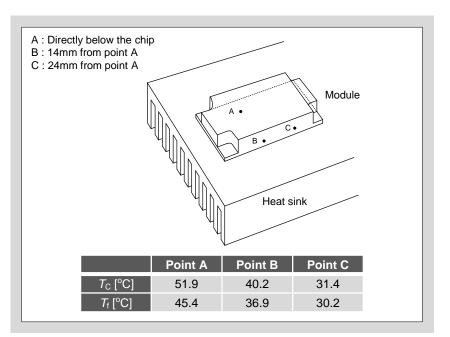

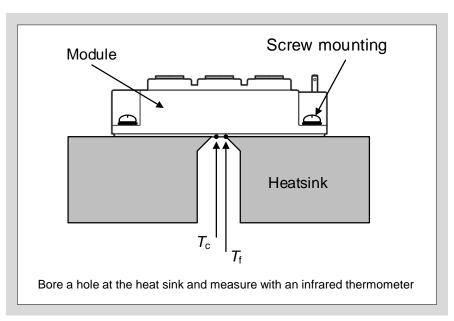

| Case temperature                       | T <sub>C</sub>                                                                        | Case temperature directly below the IGBT chip or FWD chip that generates the most heat inside the IGBT module. (refer to Chapter 6 for details.)                              |  |  |

| Storage temperature                    | $T_{ m stg}$                                                                          | Temperature range allowing storage or transportation without being subjected to electrical load.                                                                              |  |  |

| FWD <i>⁴t</i>                          | ۴t                                                                                    | Joule-integral value of overcurrent allowed that does not result in diode destruction. The overcurrent is defined by a line frequency half sine wave (50, 60Hz) at one cycle. |  |  |

| FWD surge forward current              | <b>I</b> FSM                                                                          | The maximum value of overcurrent allowed that does not result in diode destruction. The overcurrent is defined by a line frequency half sine wave (50, 60Hz).                 |  |  |

| Isolation voltage                      | V <sub>iso</sub>                                                                      | Maximum sinusoidal voltage RMS value allowed between all shorted terminals and the heat sink mounting surface.                                                                |  |  |

|                                        | Mounting                                                                              | Maximum allowable torque value when mounting the IGBT module on a heat sink with the specified screws                                                                         |  |  |

| Screw torque                           | Terminal                                                                              | Maximum allowable torque value when connecting external busbar or wires to the terminals with the specified screws                                                            |  |  |

Note 1: Values at  $T_{\rm C}$  = 25 °C unless otherwise specified

Note 2: The values listed as maximum ratings should not be exceeded under any circumstances.

Table 2-2 Electrical characteristics

| Table 2-2 Electrical Characteristics |                                      |                                    |                                                                                                                                                |  |

|--------------------------------------|--------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Term                                 |                                      | Symbol                             | Definition explanation (Refer to specifications for test conditions)                                                                           |  |

|                                      | Zero gate voltage collector current  | I <sub>CES</sub>                   | Collector current when a specific voltage is applied between C-E with G-E shorted.                                                             |  |

|                                      | Gate-Emitter<br>leakage current      | I <sub>GES</sub>                   | Gate current when a specific voltage is applied between G-E with C-E shorted.                                                                  |  |

| istics                               | Gate-Emitter threshold voltage       | V <sub>GE(th)</sub>                | G-E voltage ( $V_{\text{GE}}$ ) at a specified $I_{\text{C}}$ and C-E voltage.                                                                 |  |

| acter                                | Collector-Emitter saturation voltage | V <sub>CE(sat)</sub>               | C-E voltage at a specified collector current and G-E voltage.                                                                                  |  |

| Static characteristics               | Input capacitance                    | Cies                               | G-E capacitance when a specified voltage is applied between G-E and C-E while C-E is shorted in AC.                                            |  |

| Stati                                | Output capacitance                   | Coes                               | C-E capacitance when a specified voltage is applied between G-E and C-E while G-E is shorted in AC.                                            |  |

|                                      | Reverse transfer capacitance         | C <sub>res</sub>                   | C-G capacitance when a specified voltage is applied between G-E and C-E while G-E and C-E are shorted in AC.                                   |  |

|                                      | Forward voltage                      | $V_{F}$                            | Forward voltage of FWD at a specified forward current.                                                                                         |  |

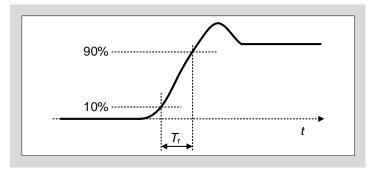

|                                      | Turn-on time                         | ton                                | The time during IGBT turn-on when $V_{\rm GE}$ rises from 10% of the maximum value until collector current rises to 90% of the maximum value.  |  |

|                                      | Rise time                            | t <sub>r</sub>                     | The time during IGBT turn-on when the collector current rises from 10 <sup>o</sup> 90% of the maximum value.                                   |  |

| tics                                 | Turn-off time                        | $t_{ m off}$                       | The time during IGBT turn-off when $V_{\rm GE}$ drops from 10% of the maximum value until collector current drops to 10% of the maximum value. |  |

| Dynamic characteristics              | Fall time                            | <b>t</b> f                         | The time during IGBT turn-off when the collector current drops from 90% to 10% of the maximum value.                                           |  |

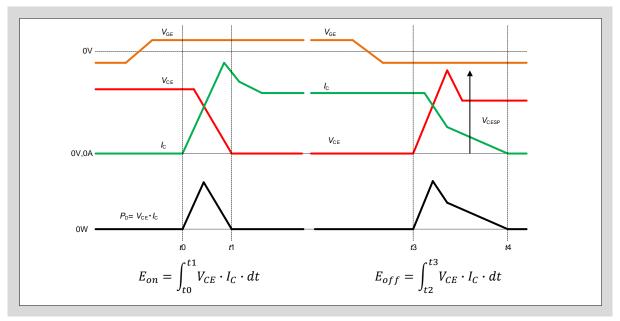

| chara                                | Turn-on loss                         | <i>E</i> <sub>on</sub>             | Loss generated during IGBT turn-on.                                                                                                            |  |

| namic                                | Turn-off loss                        | E <sub>off</sub>                   | Loss generated during IGBT turn-off.                                                                                                           |  |

| Dy                                   | Reverse recovery loss                | <i>E</i> <sub>rr</sub>             | Loss generated during FWD reverse recovery.                                                                                                    |  |

|                                      | Reverse recovery time                | t <sub>rr</sub>                    | Time required for FWD reverse recovery current to disappear.                                                                                   |  |

|                                      | Reverse recovery<br>current          | I <sub>rr</sub> (I <sub>rp</sub> ) | Peak reverse current during reverse recovery.                                                                                                  |  |

|                                      | erse bias safe<br>ating area         | RBSOA                              | Current and voltage range where IGBT can be turned off safely under specified conditions.                                                      |  |

| Inter                                | nal gate resistance                  | $r_{\rm g} R_{\rm g(int)}$         | Built-in gate series resistance.                                                                                                               |  |

| Gate charge                          |                                      | $Q_{g}$                            | Amount of charge required to turn-on the IGBT.                                                                                                 |  |

Note 1: The definition of dynamic characteristics differs between series. For details, refer to the specifications of each product.

Table 2-3 Thermal resistance characteristics

| Term               | Symbol               | Definition explanation (Refer to specifications for test conditions)                                                                             |

|--------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | R <sub>th(j-c)</sub> | Thermal resistance between the chip (junction )and case of IGBT or FWD.                                                                          |

| Thermal resistance | R <sub>th(c-s)</sub> | Thermal resistance between the case and heat sink when the IGBT module is mounted on a heat sink with the recommended torque and thermal grease. |

Table 2-4 Thermistor characteristics

| Term                  | Symbol | Definition explanation (Refer to specifications for test conditions)                                                                   |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| Thermistor resistance | R      | Thermistor resistance at specified temperature                                                                                         |

| B value               | В      | Value indicating the magnitude of thermistor resistance change between any two temperatures in resistance-temperature characteristics. |

## 2. Characteristics of IGBT and FWD

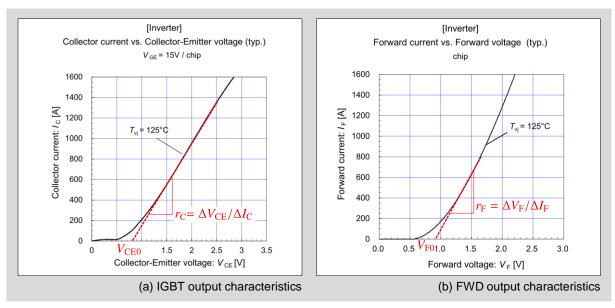

Using the 6MBI100VB-120-50 (1200V/100A, 6th generation IGBT module) as an example, the various characteristics of the IGBT described in the specifications are explained below.

#### 2.1 Static characteristics

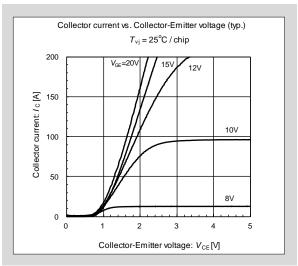

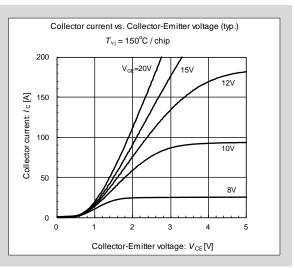

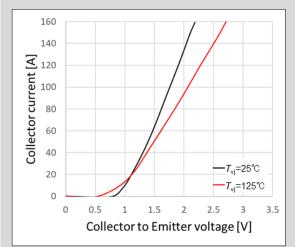

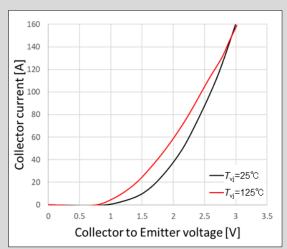

Fig. 2-1 and Fig. 2-2 show the  $V_{\rm GE}$  dependence of  $V_{\rm CE}$ - $I_{\rm C}$  characteristics (output characteristics). While the IGBT is on,  $V_{\rm CE}$  changes in accordance with  $I_{\rm C}$ ,  $V_{\rm GE}$ , and  $T_{\rm VI}$ .  $V_{\rm CE}$  represents the C-E voltage drop during the ON state, and is used to calculate the power dissipation loss of the IGBT. The smaller the  $V_{\rm CE}$  value, the lower the power dissipation loss.

It is generally recommended to operate at  $V_{\rm GE}$ =15V, and the collector current lower than the module current rating.

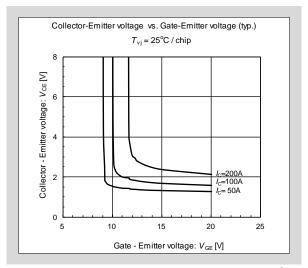

Fig. 2-3 shows the data in Fig. 2-1 as  $I_{\rm C}$  dependence of  $V_{\rm CE}$ - $V_{\rm GE}$  characteristics. From the graph, the  $V_{\rm GE}$  value limit where  $V_{\rm CE}$  suddenly increases can be read.

Fig. 2-1  $V_{CE(sat)}$  -  $I_C$  characteristics ( $T_{vi}$ =25°C)

Fig. 2-2  $V_{CE(sat)}$  -  $I_C$  characteristics ( $T_{vi}$ =150 $^{\circ}$ C)

Fig. 2-3  $V_{CE}$  -  $V_{GE}$  characteristics ( $T_{vi}$ =25°C)

#### 2.2 Switching characteristics

As the IGBT is generally used for switching applications, it is important to fully understand the turnon and turn-off switching characteristics. Since these characteristics are affected by various parameters, it is necessary to take these into consideration when determining operating conditions.

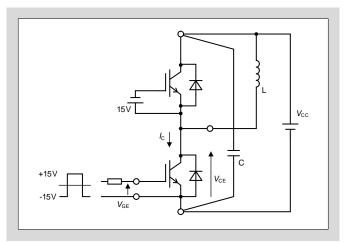

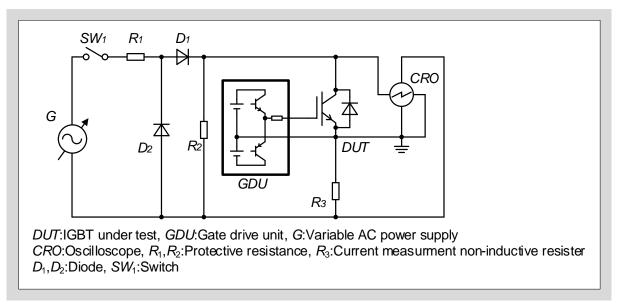

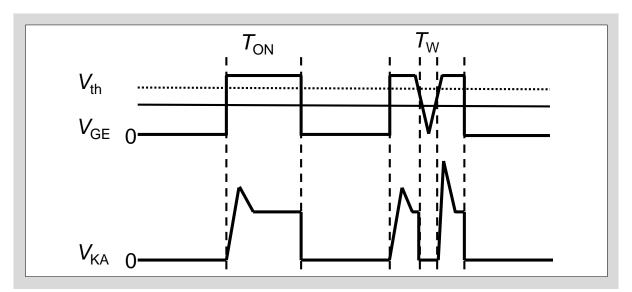

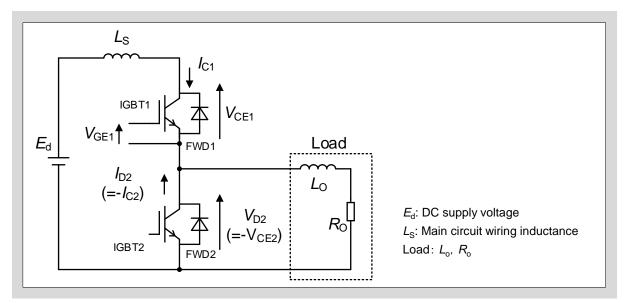

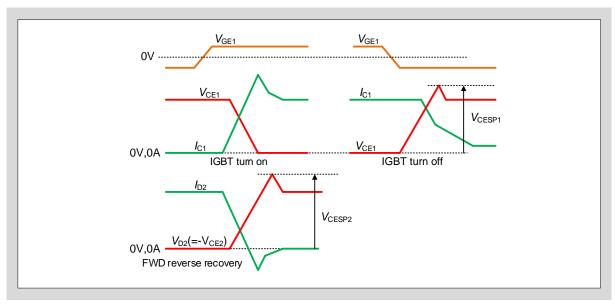

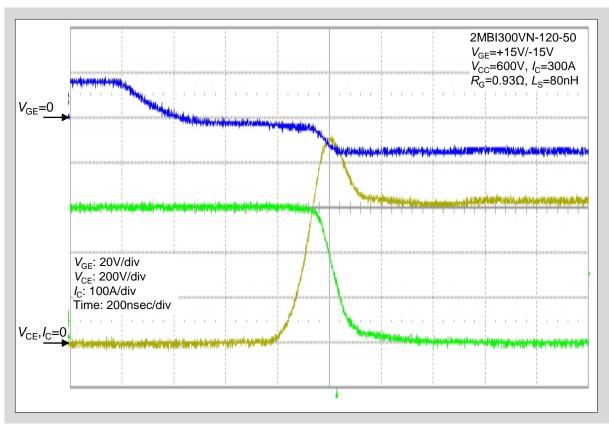

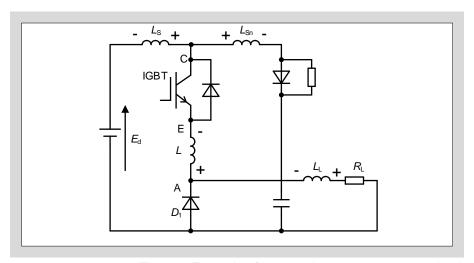

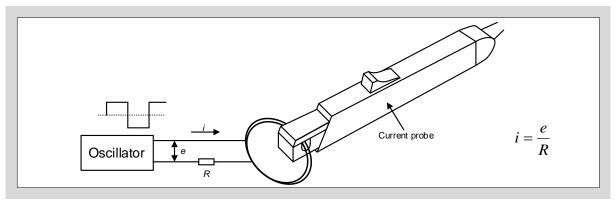

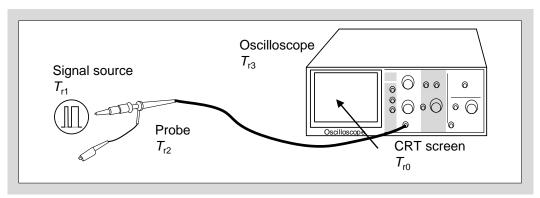

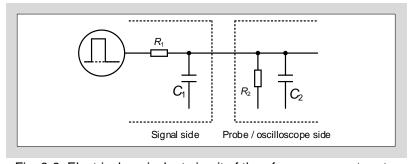

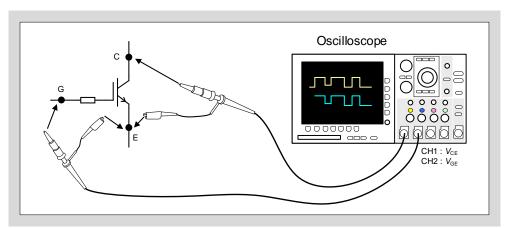

Switching characteristics can be divided into switching time and switching loss. These switching characteristics can be measured by the chopper circuit shown in Fig. 2-4.

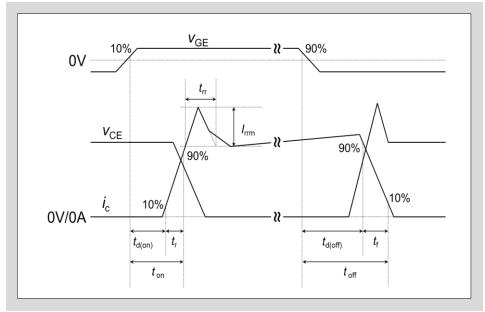

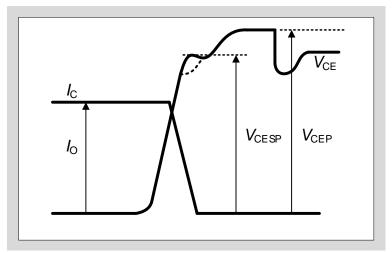

The definitions of switching times are shown in Fig. 2-5.

Fig. 2-4 Switching characteristics measuring circuit

Fig. 2-5 Definition of switching time

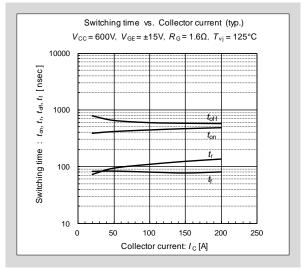

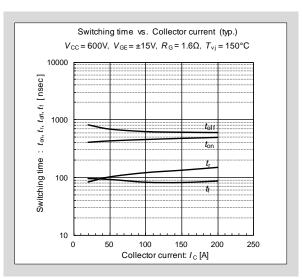

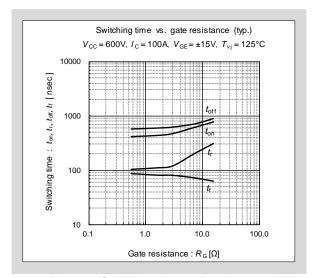

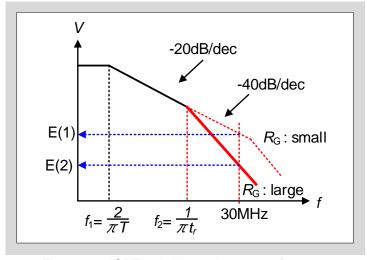

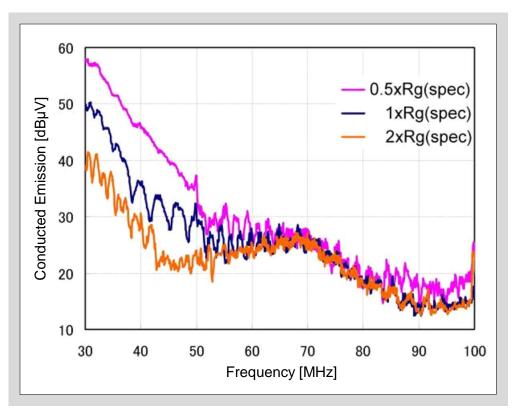

The relationship between switching time and collector current  $I_{\rm C}$  is shown in Fig. 2-6 and Fig. 2-7. Fig. 2-8 shows the relationship between switching time and gate resistance  $R_{\rm G}$ . As shown in these figures, the switching time varies depending on  $I_{\rm C}$ ,  $T_{\rm vj}$ , and  $R_{\rm G}$ , so please take this into consideration when designing equipment.

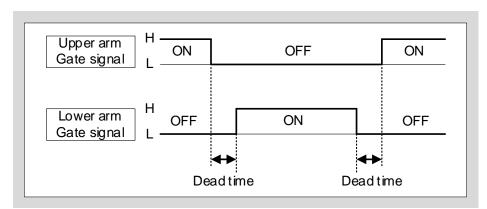

For example, when the IGBT is used under the condition that  $t_{\text{off}}$  is too long, it may exceed the dead time and cause a series arm short-circuit.

It is also important to be aware that if the switching time, such as  $t_i$  is too short, the transient current change rate  $dI_C/dt$  will increase and may cause a high turn-off surge voltage (= $L_S \cdot dI_C/dt$ ). Since this surge voltage is superimposed on the applied voltage, the resulting voltage might exceed RBSOA and destroy the IGBT (refer to Chapter 2 and 4 for details).

Fig. 2-6 Switching time -  $I_{\rm C}$  characteristics  $(T_{\rm vi}=125^{\rm o}{\rm C})$

Fig. 2-7 Switching time -  $I_C$  characteristics  $(T_{vi}=150^{\circ}C)$

Fig. 2-8 Switching time -  $R_G$  characteristics ( $T_{vi}$ =125°C)

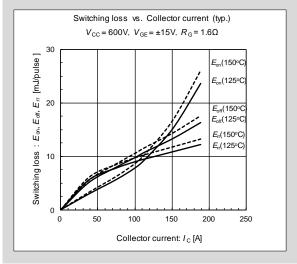

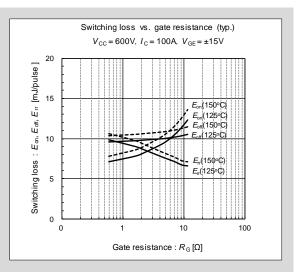

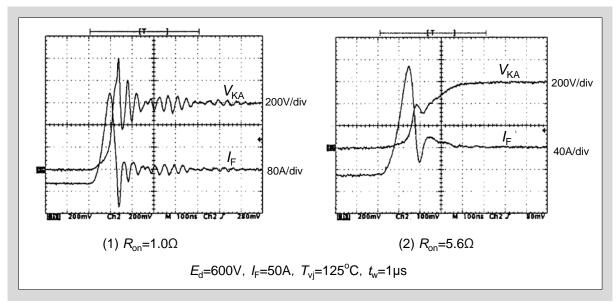

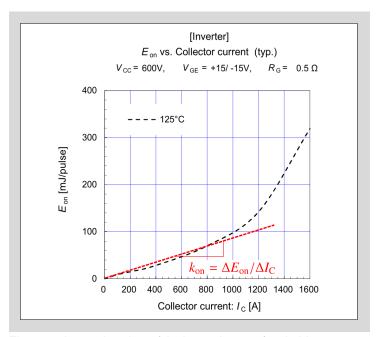

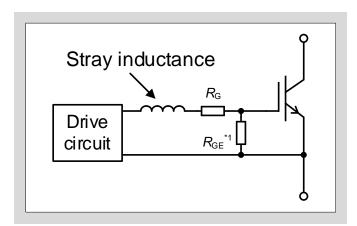

Switching loss ( $E_{\rm on}$ ,  $E_{\rm off}$ ,  $E_{\rm rr}$ ) occurs every time an IGBT is turned on or off, therefore it is important to minimize this loss as much as possible. As shown in Fig. 2-9 and 2-10, switching loss changes in accordance with  $I_{\rm C}$ ,  $T_{\rm vj}$ , and  $R_{\rm G}$ . In particular, the selection of  $R_{\rm G}$  is important. If it is too large, the switching loss will increase, and series arm short circuit due to the aforementioned insufficient dead time will easily occur. Conversely, if  $R_{\rm G}$  is reduced to reduce switching loss, the aforementioned excessive surge voltage (= $L_{\rm S}$ ·d $I_{\rm C}$ /d $I_{\rm C}$ ) may occur.

As can be seen from this, the value of main circuit inductance  $L_S$  has great influence on  $R_G$  selection. The smaller the value is, the smaller the surge voltage will be, making it easier to consider  $R_G$  selection. Therefore, it is recommended to design the  $L_S$  value as small as possible.

When selecting  $R_{\rm G}$ , it is also necessary to consider matching with the capacitance of the IGBT drive circuit. Therefore, please select the  $R_{\rm G}$  after careful consideration using the capacitance characteristics as shown in Chapter 2.3.

Fig. 2-9 Switching loss - I<sub>C</sub> characteristics

Fig. 2-10 Switching loss - R<sub>G</sub> characteristics

#### 2.3 Capacitance characteristics

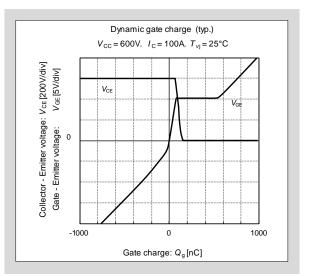

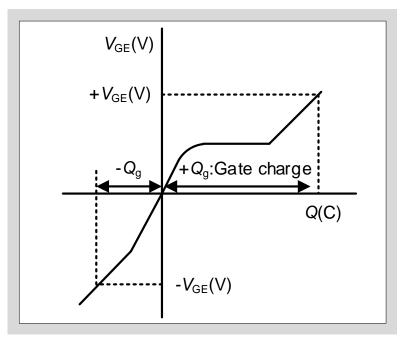

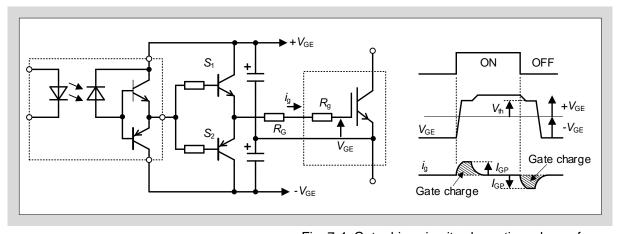

Fig. 2-11 shows the characteristics of  $Q_{\rm g}$ . This characteristic shows the change of  $V_{\rm CE}$ ,  $V_{\rm GE}$  with respect to  $Q_{\rm g}$ . ' $Q_{\rm g}$  increases' means 'charging the G-E capacitance of the IGBT', so when  $Q_{\rm g}$  increases,  $V_{\rm GE}$  (= $Q_{\rm g}$  / G-E capacitance) rises and the IGBT turns on. When the IGBT turns on,  $V_{\rm CE}$  drops to the saturation voltage. Thus,  $Q_{\rm g}$  indicates the amount of charge required to drive the IGBT. Use this characteristic when determining the power supply capacity of the drive circuit.

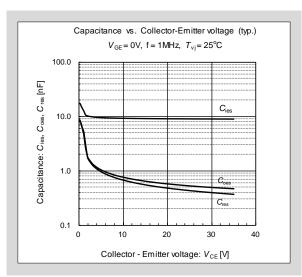

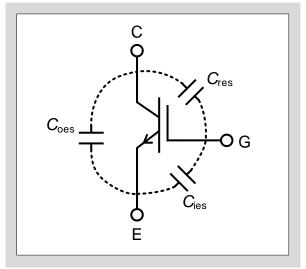

Fig. 2-12 shows the IGBT junction capacitance characteristics. Fig. 2-13 shows the junction capacitance  $C_{\text{ies}}$ ,  $C_{\text{oes}}$  and  $C_{\text{res}}$ . Use these characteristics along with  $Q_{\text{q}}$  to design your drive circuit.

Fig. 2-11  $V_{CE}$ ,  $V_{GE}$  -  $Q_g$  characteristics

Fig. 2-12 Junction capacitance characteristic

Fig. 2-13 Junction capacitance

#### 2.4 Reverse biased safe operating area

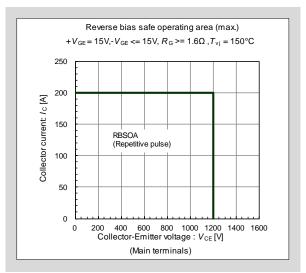

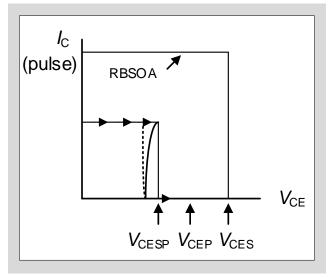

During turn-off, IGBT has a safe operating area defined by  $V_{\rm CE}$  an  $I_{\rm C}$  called RBSOA (Reverse Bias Safe Operating Area). Fig. 2-14 shows the area of 1200V/100A IGBT as an example.

It is important to design the snubber circuit that will keep  $V_{\text{CE}}$  and  $I_{\text{C}}$  within the region of RBSOA when the IGBT is turned off. In the case of a short circuit (non-repetitive), the IGBT safe operating area defined by  $V_{\text{CE}}$  an  $I_{\text{C}}$  is called SCSOA (Short Circuit Safe Operating Area). SCSOA is different for each IGBT series, thus refer to the technical data of each series for details.

Fig. 2-14 RBSOA

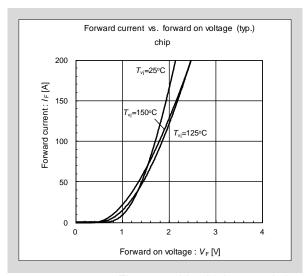

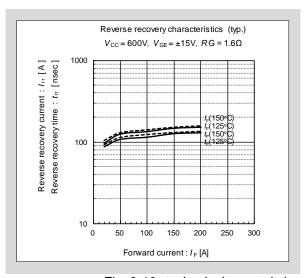

#### 2.5 FWD characteristics

The IGBT module has built-in anti-parallel FWD. Fig. 2-15 shows the FWD  $V_F$ - $I_F$  characteristic, and Fig. 2-16 shows the reverse recovery characteristic ( $t_{rr}$ ,  $I_{rr}$ ).  $E_{rr}$  characteristics are shown in Fig. 2-9 and 2-10. Use these characteristics to calculate the power loss of FWD as well as the IGBT. Note that these characteristics change in accordance with  $I_F$ ,  $T_{vi}$ , and  $R_G$ .

Fig. 2-15  $V_F$  -  $I_F$  characteristics

Fig. 2-16  $t_{rr}$ ,  $I_{rr}$  -  $I_{F}$  characteristics

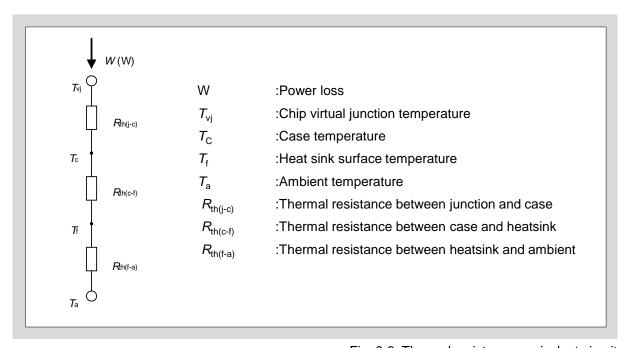

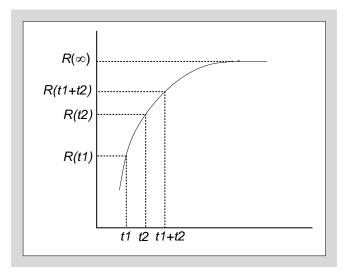

#### 2.6 Transient thermal resistance characteristics

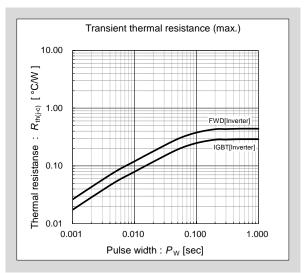

Fig. 2-17 shows the transient thermal resistance characteristics used for temperature rise calculation and heat sink design (this characteristic is for one arm for both IGBT and FWD).

This thermal resistance is a characteristic often used in thermal analysis, and the formula is very similar to Ohm's law of electrical resistance. It is defined as:

Temperature difference  $\Delta T$  [°C] = Thermal resistance  $R_{th}$  [°C / W] x Energy E (loss) [W]

In the IGBT module, the thermal resistance is used when calculating the  $T_{vj}$  of the IGBT and FWD. (For details, refer to Chapter 6 'Cooling Design')

Fig. 2-17 Transient thermal resistance

## Chapter 3 IGBT Module Selection and Application Notes

| Selection of IGBT Module Ratings       | 3-2  |

|----------------------------------------|------|

| 2. Static Electricity Countermeasures  | 3-4  |

| 3. Protection Circuits Design          | 3-5  |

| 4. Cooling Design                      | 3-5  |

| 5. Gate Drive Circuits Design          | 3-5  |

| 6. Parallel Connection                 | 3-6  |

| 7. Mounting Notes                      | 3-6  |

| 8. Storage and Transportation Notes    | 3-8  |

| 9. Reliability Notes (Lifetime Design) | 3-9  |

| 10. Other Precautions                  | 3-10 |

This chapter describes the precautions when using IGBT module and application.

## 1. Selection of IGBT Module Ratings

When using IGBT modules, it is important to select modules with the voltage and current ratings most suited for the intended application.

#### 1.1 Voltage rating

The IGBT must have voltage rating that is suitable with the input voltage of the system in which it will be installed. Table 3-1 shows the IGBT voltage ratings and applicable input voltages. Use this table as a reference when selecting modules for a particular voltage application.

Table 3-1 IGBT rated voltage and application input voltage

|                                     | Area -        |             |                         | IGBT rated voltage |                                                                          |

|-------------------------------------|---------------|-------------|-------------------------|--------------------|--------------------------------------------------------------------------|

|                                     |               |             | 600V                    | 1200V              | 1700V                                                                    |

|                                     | Asia          | Japan       | 200VAC                  | 400VAC, 440VAC     | 690VAC (Industry high voltage power supply, wind power generation, etc.) |

| oply (e                             |               | South Korea | 200VAC, 220VAC          | 380VAC             |                                                                          |

| r sug                               |               | China       | 220VAC                  | 380VAC             |                                                                          |

| Commercial power voltage (input vol | North America | U.S.A       | 120VAC, 208V,<br>240VAC | 460VAC, 480VAC     |                                                                          |

|                                     | Europe        | U.K.        | 230VAC                  | 480VAC             |                                                                          |

|                                     |               | France      | 230VAC                  | 400VAC             |                                                                          |

|                                     |               | Germany     | 230VAC                  | 400VAC             |                                                                          |

|                                     |               | Russia      | 220VAC                  | 380VAC             |                                                                          |

#### 1.2 Current rating

When the collector current  $I_{\rm C}$  of the IGBT module increases, the conduction loss and switching loss increase, resulting in an increase in the module temperature. Since the IGBT module must be used with the virtual junction temperature  $T_{\rm vj}$  of IGBT and FWD below the maximum virtual junction temperature  $T_{\rm vi(max)}$ ,  $I_{\rm C}$  must be set in order not to exceed  $T_{\rm vi(max)}$ .

Incorrect selection of current rating may lead to module destruction or deterioration of reliability. Note that in high frequency switching applications, switching loss increases, which increases the module temperature.

As a basic selection criteria, it is common to select a module with current rating higher than  $\sqrt{2}$  times of the AC output current RMS value of the inverter circuit. However, the selection of the current rating depends on the operating conditions and heat dissipation conditions of the equipment, thus it is important to select the current rating after checking the power loss and temperature rise in the equipment.

#### 1.3 Maximum rating

Use the product within the maximum ratings (voltage, current, temperature, etc.) described in the specifications. Using the product beyond the maximum rating may destroy the product. Also, the value described in each item of the absolute maximum rating is specified for that item, not for combination of more than one item.

#### 1.4 RBSOA

Make sure that the IGBT turn-off voltage and current operating trajectories are within the RBSOA specifications. Using the IGBT beyond the RBSOA region may destroy the product.

#### 1.5 Diode inrush current

When using the rectifier diode or FWD for rectifier application, a large inrush current will flow to charge the DC smoothing capacitor when the power is turned on. The guaranteed values for this inrush current are expressed as  $I_{\text{FSM}}$  (non-repetitive) and Pt (non-repetitive). However, if inrush current flows frequently into the product, the product may be destroyed due to power cycle destruction by the repetitive current. For applications where such inrush current flows frequently, take measures to suppress the inrush current to prevent power cycle destruction.

Note that inrush current may flow to charge the capacitor too when an instantaneous voltage drop occurs in the power supply system.

On the other hand, if transient surge voltage due to lightning strike, etc. that exceeds the voltage rating of the product is applied to the product, the product might be destroyed. Thus, if surge voltage is expected, insert surge protection devices to suppress the voltage to within the product specifications.

### 2. Static Electricity Countermeasures

Generally, the absolute maximum rating of  $V_{\rm GE}$ ,  $V_{\rm GES}$  is ±20V. If voltage exceeding  $V_{\rm GES}$  is applied to G-E, the IGBT gate may be destroyed. Therefore, ensure that  $V_{\rm GE}$  value does not exceed  $V_{\rm GES}$ .

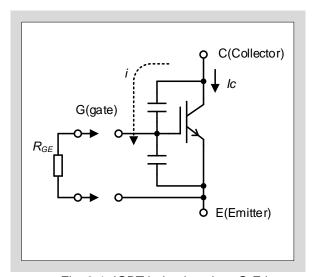

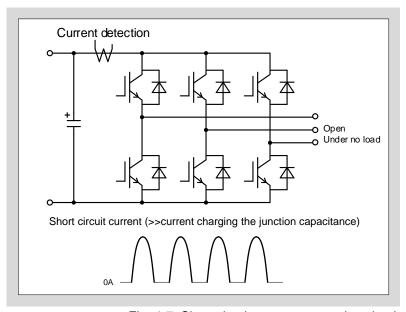

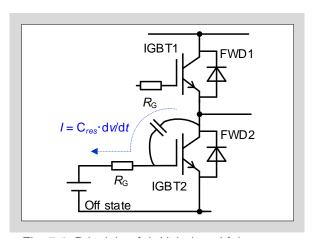

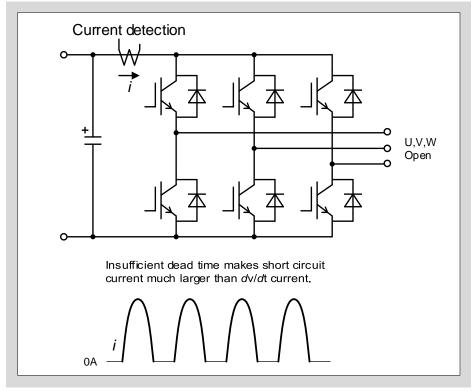

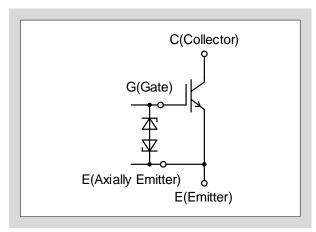

If voltage is applied between C-E of IGBT while G-E is open as shown in Fig. 3-1, the IGBT may be destroyed. This is because the current *i* flows from the collector to the gate due to changes in the collector voltage, causing the gate voltage to rise and turn-on the IGBT. As a result, collector current will flow and the IGBT could overheat and be destroyed.

For this reason, after installing an IGBT module, if the gate circuit is malfunctioning or completely inoperative (gate is open), the IGBT may be destroyed when voltage is applied to the main circuit. In order to prevent this, it is recommended to connect a  $10k\Omega$  resistor ( $R_{GE}$ ) between G-E.

Fig. 3-1 IGBT behavior when G-E is open

Furthermore, the IGBT gate is very sensitive to static electricity. Observe the following precautions when handling the product.

- (1) When handling IGBT modules after unpacking, discharge any static electricity from your body and clothes by grounding through a high resistance (1MΩ). Then, any handling of IGBTs should be done while standing on a grounded conductive mat.

- (2) The terminals of IGBT modules are not protected against static electricity. When handling, hold them by the module case and do not touch the terminals (especially the control terminals).

- (3) When soldering the terminals, ground the tip of the soldering iron through a low resistance to protect the module from static electricity.

## 3. Protection Circuits Design

Since IGBT modules may be destroyed by overcurrent, overvoltage or other abnormality, it is necessary to design protection circuits.

It is important to fully understand the IGBT modules characteristics when designing these circuits. An inappropriate circuit will not be able to protect the module. For example, the overcurrent cut-off time may be too long, or the capacitance of the snubber capacitor may be too small.

For more details on overcurrent and overvoltage protection methods, refer to Chapter 5 'Protection Circuit Design' of this manual.

## 4. Cooling Design

IGBT modules have a maximum virtual junction temperature ( $T_{vj(max)}$ ). An appropriate heat sink must be selected to keep the temperature below this value. When designing heat sink, the operating conditions of the IGBT module has to be fully considered.

First, calculate the loss of the IGBT module. Based on that loss, select a heat sink that will keep T<sub>vi</sub> below the limit. If the heat sink design is insufficient, the temperature may exceed  $T_{\rm vi(max)}$  during operation and destroy the module. For more information on IGBT power loss calculation and heat sink selection methods, refer to Chapter 6 'Cooling Design' of this manual.

## 5. Gate Drive Circuits Design

It is no exaggeration to say that the design of the gate drive circuits ultimately determines the performance of the IGBT. It is also closely related to the protection circuits design.

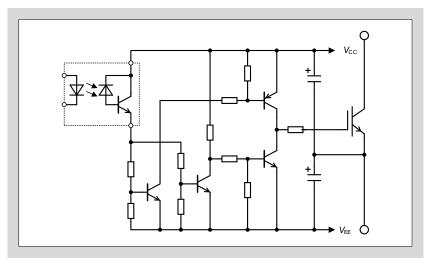

Gate drive circuits consists of a forward bias circuit to turn-on the IGBT, and a reverse bias circuit to turn-off and keep the IGBT in a stable off state. The characteristics of the IGBT change in accordance with each bias condition.

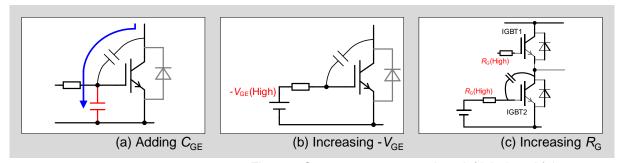

Insufficient reverse bias gate voltage - $V_{\rm GE}$  may cause false turn-on. Set a sufficient - $V_{\rm GE}$  value to prevent false turn-on. If the dv/dt is high, false turn-on of the opposing arm IGBT, gate overvoltage, or noise propagation to the power supply line may occur. Set the optimum drive conditions ( $+V_{GE}$ ,  $-V_{GE}$ )  $R_{\rm G}$ ,  $C_{\rm GE}$ ) to avoid these problems.

Also, if the wiring length between the IGBT module and the gate drive circuit is long, the gate voltage at the product terminal may fluctuate and the product may be destroyed by overvoltage.

For more information on how to design the best gate drive circuits, refer to Chapter 7 'Gate Drive Circuit Design' of this manual.

### 6. Parallel Connection

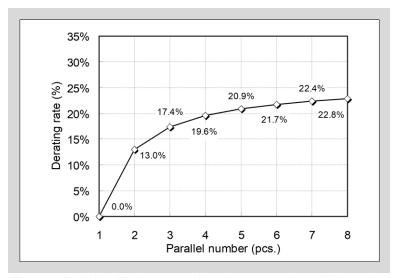

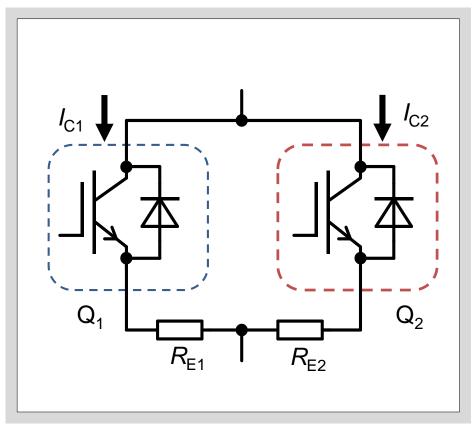

In high capacity inverters and other equipment that needs to control large currents, it may be necessary to connect IGBT modules in parallel.

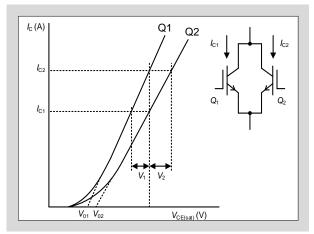

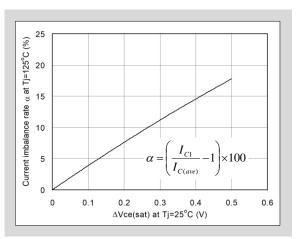

In parallel connection, it is important that the circuit design allows an equal flow of current to each of the modules. If the current is not balanced among the IGBTs, a higher current may concentrate in one IGBT and destroy it.

The electrical characteristics of each module as well as the wiring design determines the current balance between parallel modules. Thus, it is necessary to design such that the C-E saturation voltage  $V_{CE(sat)}$  of each parallel modules is matched and the main circuit wiring is symmetrical.

For a detailed explanation, refer to Chapter 8 "Parallel Connections" of this manual.

Note that the 6-Pack, PIM, IPM, and Small IPM are not designed on the premise of using in parallel connections, thus application of these modules in parallel connections are not guaranteed.

### 7. Mounting Notes

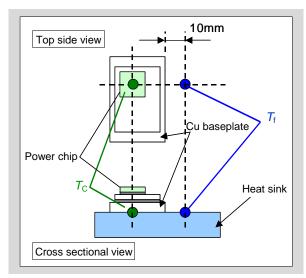

#### 7.1 Mounting to heat sink

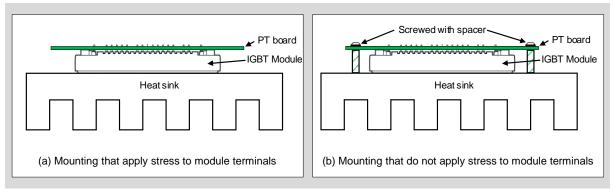

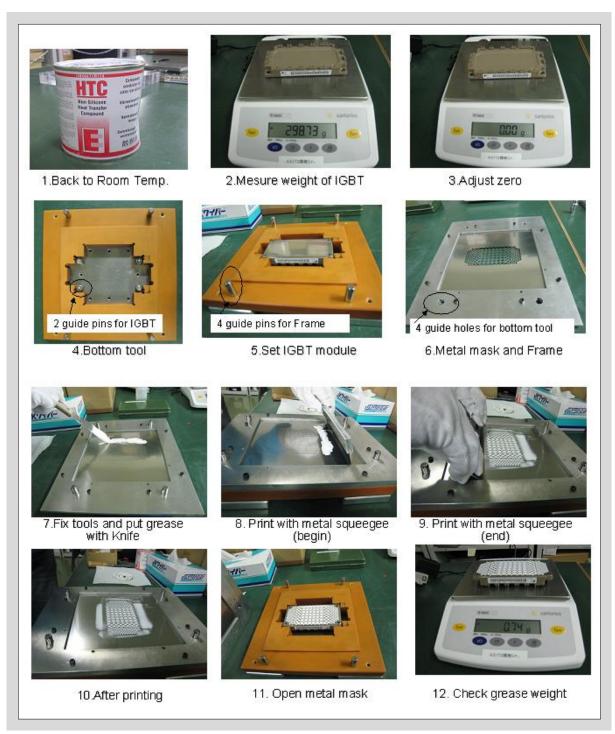

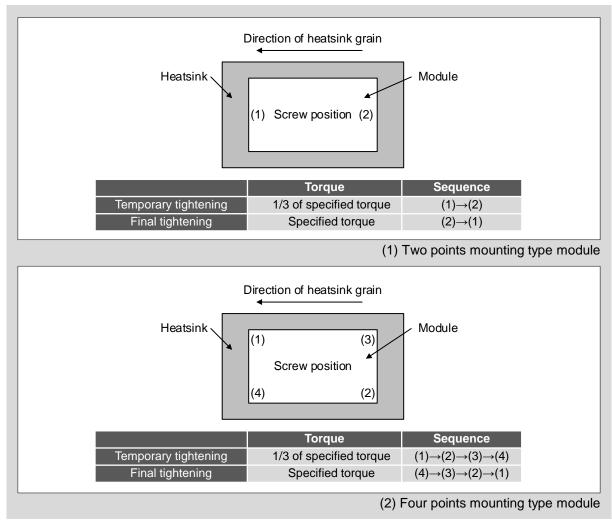

When mounting the product to heat sink, it is recommended to apply thermal grease to the module's base plate to ensure heat dissipation. In order to spread the thermal grease evenly, the flatness and surface roughness of the heat sink should be within the range of the recommended values described in the specifications.

If the amount and application method of the thermal grease are not appropriate, it may prevent the thermal grease from spreading over the entire module's base plate, resulting in poor heat dissipation and lead to thermal failure. To determine whether the amount of thermal grease applied and the method of application is appropriate, confirm that the thermal grease has spread over the entire base plate of the product. (You can check the extent of spreading by removing the module after mounting)

If the amount of thermal grease near the product mounting hole is excessive, the thermal grease will act as a spacer, hindering the spread of the thermal grease and causing deterioration in heat dissipation.

Also, depending on the properties of the thermal grease and application method, the thermal grease may deteriorate or deplete during high temperature operation and temperature cycles, shortening the product lifetime. Thus, pay attention to the selection and application method of thermal grease.

The surface flatness of the heat sink between the screw mounting holes should be 50µm or less per 100mm, and the surface roughness should be 10µm or less. Excessive convex warpage may cause insulation failure of the product, leading to serious accidents. On the other hand, excessive concave warpage or distortion will create gaps between the IGBT module and the heat sink, which will result in poor heat dissipation and may lead to thermal failure.

Refer to the mounting instruction of each package for details on how to select and apply thermal grease, and how to mount the product to heat sink.

Note that the surface flatness and roughness requirements for heat sinks of PrimePACK<sup>TM\*</sup> differ from other products. Refer to the mounting instruction for details.

\*PrimePACK<sup>TM</sup> is a registered trademark of Infineon Technologies

#### 7.2 Terminal connections

During soldering of the IGBT module terminals, note that soldering at an excessively high temperatures may cause deterioration of the package. If reflow soldering method is used, the solder inside the IGBT module may remelt and affect its reliability. In this case, Fuji Electric Co., Ltd. is not responsible for the product performance and appearance.

If the applied bus bars are not suitable, the temperature of the main terminals may rise above the storage temperature. Use the main terminals within the storage temperature range.

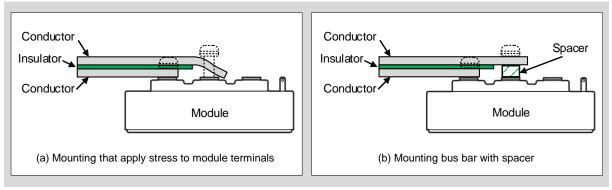

Applying excessive stress (tensile, pushing, bending) to the main terminals and control terminals may deform the terminals and crack the case resin, resulting in poor contact and poor insulation. Refer to the mounting instructions of each package for the maximum allowable stress on the main and control terminals.

For screw type terminals, tighten the screws with the specified tightening torque. If the tightening torque is excessive, insulation failure may occur due to cracking of the case. If the tightening torque is small, the contact resistance may increase, resulting in increased heat generation at the terminals. In addition, it is expected that the screws may loosen due to vibration, etc., thus select and use screws that are difficult to loosen, tighten with the appropriate torque, and perform retightening to suppress the occurrence.

Refer to the outline drawing in the specifications and select screws with the appropriate length. If the screw length is longer than the allowable value, the product may be damaged, resulting in ground fault or insulation failure. In such cases, Fuji Electric will not be held responsible.

If the printed circuit board is not suitable, the temperature of the main terminal pins may rise above the storage temperature. Use the main terminal pins within the storage temperature range.

Applying excessive stress (tensile, pushing, bending) to the main terminals and control terminals may deform the terminals and crack the case resin, resulting in poor contact and poor insulation. Refer to the mounting instructions of each package for the maximum allowable stress on the main and control terminals.

Do not apply stress that causes the lid to deform. The internal circuit of the product may be damaged in the pushing direction. In addition, the lid may come off in the pulling direction.

## 8. Storage and Transportation Notes

#### 8.1 Storage

- (1) The products should be stored at an ambient temperature of 5 to 35°C and humidity of 45 to 75%. If the storage area is very dry, a humidifier may be required. In such case, use only deionized water or boiled water, since the chlorine in tap water may corrode the product terminals.

- (2) Avoid exposure to corrosive gases and dust.

- (3) Rapid temperature changes may cause condensation on the product surface. Avoid such environment and store products in a place with minimal temperature changes.

- (4) Do not apply external force to the products during storage. Unexpected force may be applied to the products when stacked. Do not place heavy objects on the products.

- (5) Store the products with unprocessed terminals. Storing after the terminals are processed may cause soldering defects later during product mounting due to rust.

- (6) Use only antistatic containers or the same container as shipped for storing the products in order to prevent ESD damage.

- (7) Use grounded metal storage shelves.

#### 8.2 Transportation

- (1) Avoid extreme forces such as dropping or shock when transporting the products .

- (2) When transporting several products in the same box or container, insert padding between the products to protect the terminals and to keep the products from shifting.

- (3) Take measures against static electricity from being applied to the gate terminals, such as using antistatic bag or shorting the gate and emitter with aluminum foil when transporting the product.

## 9. Reliability Notes (Lifetime Design)

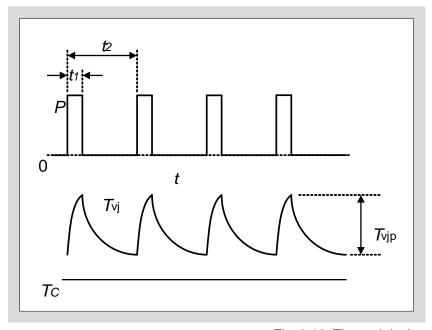

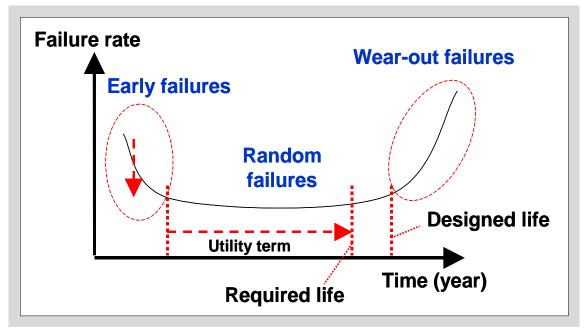

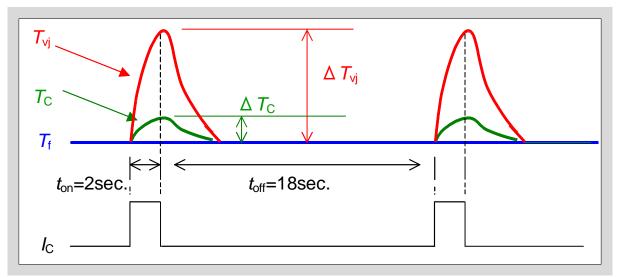

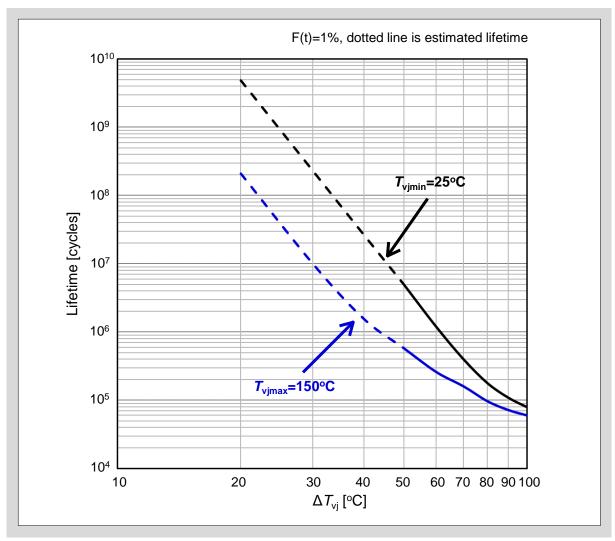

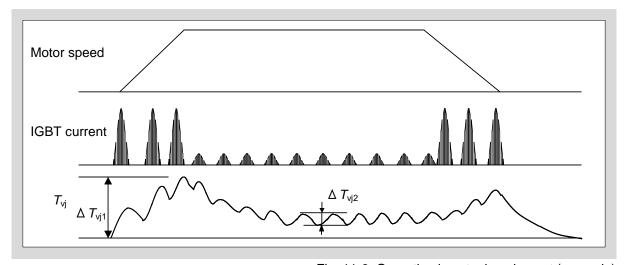

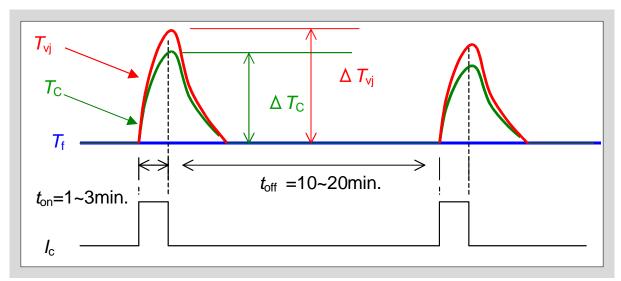

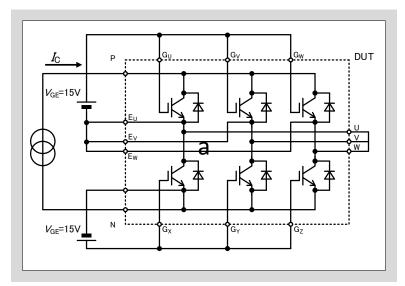

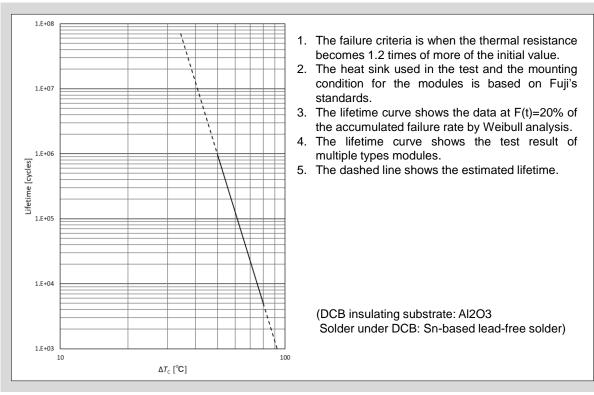

Generally, during the operation of power converters such as inverters, the temperature of the IGBT module  $T_{v_j}$  rises and falls repeatedly. This temperature change  $\Delta T_{v_j}$  causes the IGBT module to be exposed to thermal stress, which may shorten its lifetime depending on the operating conditions. Therefore, it is necessary to design the lifetime of the IGBT module to be longer than that of the power converters.

In most cases, the temperature change of the IGBT module is checked and the lifetime design is performed based on the power cycling (P/C) capability. If the lifetime design is insufficient, the lifetime of the IGBT module may be shorter than the required lifetime, and the module reliability may not be ensured. Therefore, it is important to design the IGBT module lifetime so that it meets the required reliability. For more detailed information on reliability notes, refer to Chapter 11 'Reliability of Power Modules' of this manual.

Please use the IGBT module within the  $\Delta T_{vj}$  P/C lifetime shown in Fig. 11-5. However, Fig. 11-5 shows the  $\Delta T_{vj}$  P/C lifetime of the V series IGBT modules. The  $\Delta T_{vj}$  P/C lifetime of the X series is different. Please refer to the technical data for details. In addition to this  $\Delta T_{vj}$  P/C, there is another P/C based on the case temperature change of the module,  $\Delta T_{C}$  P/C. Since the  $\Delta T_{C}$  P/C lifetime depends on the thermal stress caused by the rise and fall of the case temperature, the lifetime of the IGBT module is greatly affected by the cooling design of the equipment. If the case temperature rises and falls frequently, pay sufficient attention to the product lifetime.

If the IGBT module is used beyond its lifetime, product quality deterioration may occur. In the worst case, the IGBT module may be destroyed. Please fully understand the usage environment of the equipment in which the IGBT module is to be installed, and apply the IGBT module after considering whether the target lifetime can be satisfied.

### 10. Other Precautions

Be sure to install an adequate fuse or circuit breaker between the power supply and the product in case the product is destroyed by an unexpected accident to prevent secondary destruction such as fire, explosion, and spread of fire.

In environments containing acids, alkalis, organic substances, corrosive gases (hydrogen sulfide, sulfurous acid gas, etc.), and corrosive liquids (cutting fluid, etc.), the product may oxidize or corrode, resulting in poor contact, disconnection, short circuit, ground fault, etc. In such cases, do not use the product as it may cause malfunctions. Should a short circuit or ground fault occurs, there is a secondary risk of smoke, fire, or explosion. If the product is used under conditions containing these corrosive substances, Fuji Electric Co., Ltd. is not responsible regardless of the conditions (temperature, humidity, concentration, etc.).

If the product is to be operated after being stored or assembled in a high humidity environment, operate the equipment after removing the moisture sufficiently. If the product is operated in a moisture-absorbed state, it may cause electrical wiring defects or insulation failures inside the product, in which case Fuji Electric Co., Ltd. is not responsible.

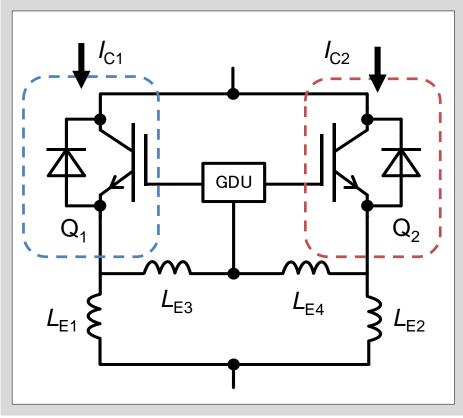

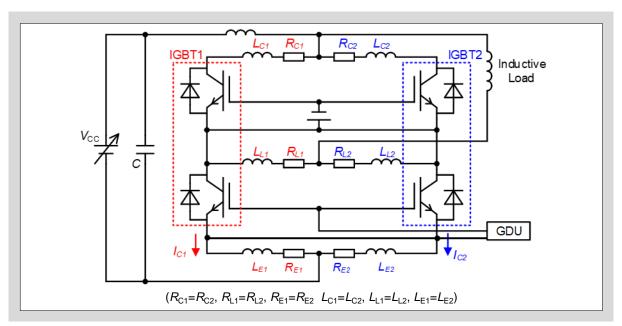

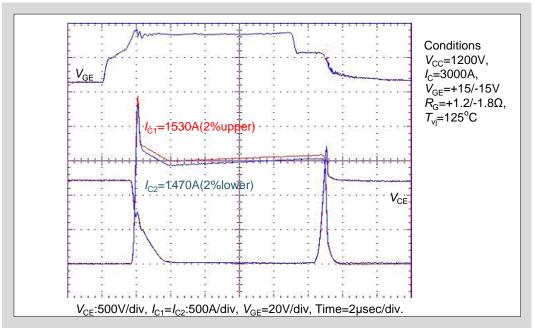

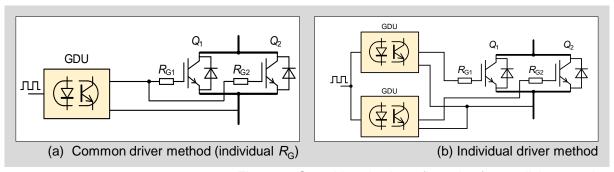

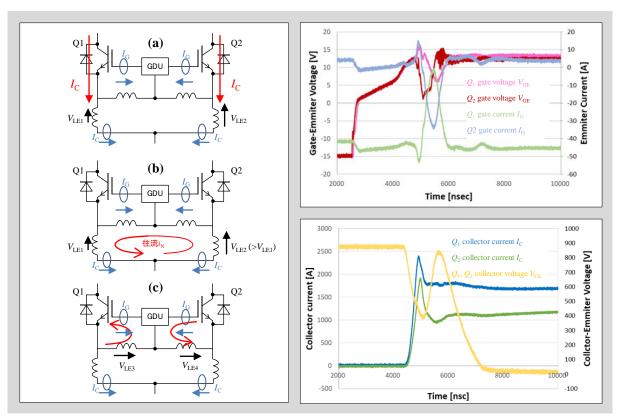

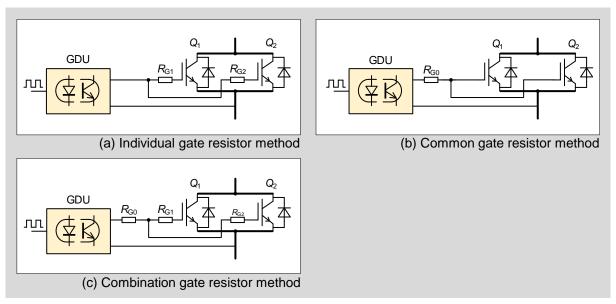

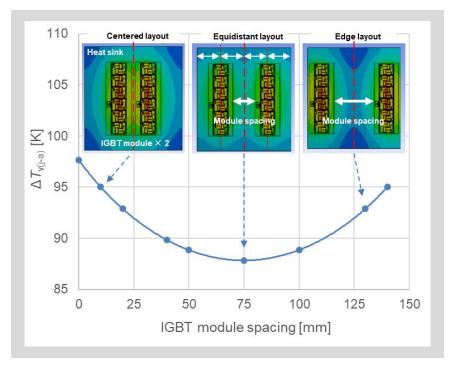

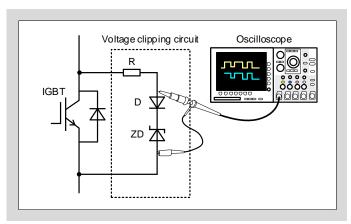

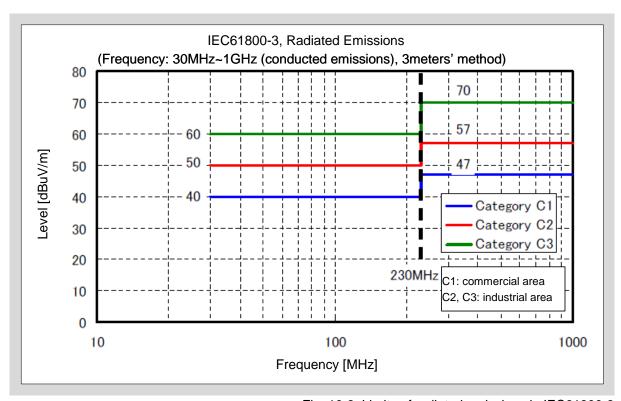

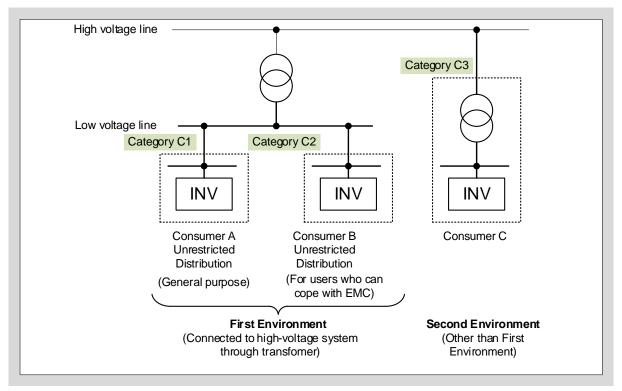

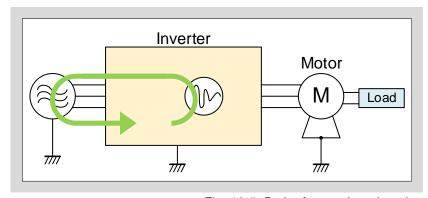

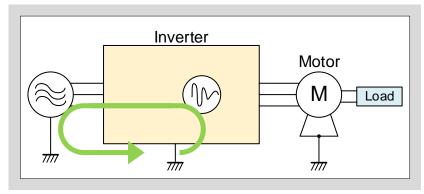

The products are not designed for use in dusty environments. If it is used in an environment where dust is generated, heat dissipation may deteriorate due to the heat sink may become clogged, and short circuits or ground faults may occur due to leaks between terminals or creeping discharge. (Even if the dust is an insulating material such as fiber, it may leak due to moisture absorption.)