# Fuji IGBT Intelligent-Power-Module

"Compact Type" (Preliminary)

# **Application Note**

6MBP15VS\*060-50 6MBP20VS\*060-50 6MBP30VS\*060-50

Fuji Electric Co., Ltd. Jun. 2015

# CONTENTS

### **Chapter 1 Product Outline**

| 1. Introduction                             | 1-2 |

|---------------------------------------------|-----|

| 2. Product line-up                          | 1-4 |

| 3. Definition of Type Name and Marking Spec | 1-5 |

| 4. Package outline dimensions               | 1-6 |

| 5. Absolute Maximum Ratings                 | 1-7 |

### Chapter 2 Description of Terminal Symbols and Terminology

| 1. Description of Terminal Symbols | 2-2 |

|------------------------------------|-----|

| 2. Description of Terminology      | 2-3 |

### Chapter 3 Detail of Signal Input/Output Terminals

| 1. Control Power Supply Terminals VCCH, VCCL, COM | 3-2  |

|---------------------------------------------------|------|

| 2. Power Supply Terminals of High Side VB(U,V,W)  | 3-6  |

| 3. Function of Internal BSDs (Boot Strap Diodes)  | 3-9  |

| 4. Input Terminals IN(HU,HV,HW), IN(LU,LV,LW)     | 3-13 |

| 5. Over Current Protection Input IS               | 3-16 |

| 6. Fault Status Output VFO                        | 3-17 |

| 7. Linear Temperature Sensor Output TEMP          | 3-18 |

| 8. Over Heat Protection                           | 3-20 |

### **Chapter 4 Power Terminals**

| 1. Connection of Bus Input terminal and Low Side Emitters | 4-2 |

|-----------------------------------------------------------|-----|

| 2. Setting of Shunt Resister of Over Current Protection   | 4-3 |

### Chapter 5 Recommended wiring and layout

| 1. | Examples of Application Circuits             | 5-2 |

|----|----------------------------------------------|-----|

| 2. | Recommendation and Precautions in PCB design | 5-5 |

### Chapter 6 Mounting Guideline and Thermal Design

| 1. Soldering to PCB             | 6-2 |

|---------------------------------|-----|

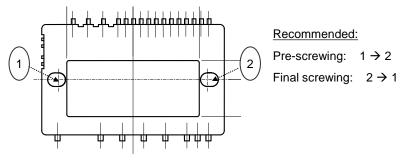

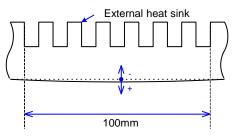

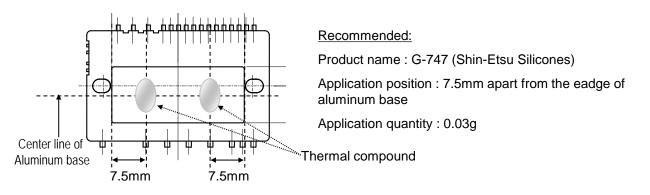

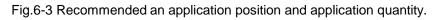

| 2. Mounting to Heat sink        | 6-3 |

| 3. Cooler (Heat Sink) Selection | 6-4 |

### **Chapter 7 Cautions**

| 1. Other warnings and precautions | 7-2 |

|-----------------------------------|-----|

| 2. Notice                         | 7-3 |

# Chapter 1

# **Product Outline**

| Contents                                    | Page |

|---------------------------------------------|------|

| 1. Introduction                             | 1-2  |

| 2. Product line-up                          | 1-4  |

| 3. Definition of type name and marking spec | 1-5  |

| 4. Package outline dimensions               | 1-6  |

| 5. Absolute maximum ratings                 | 1-7  |

|                                             |      |

# 1. Introduction

The objective of this document is introducing Fuji IGBT Intelligent-Power-Module "Compact Type".

At first, the product outline of this module is described.

Secondary, the terminal symbol and terminology used in this note and the specification sheet are explained. Next, the design guideline on signal input terminals and power terminals are shown using its structure and behavior. Furthermore, recommended wiring and layout, and the mount guideline are given.

### Feature and functions

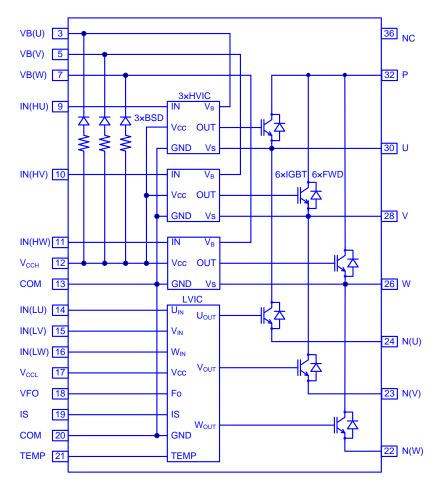

1.1 Built-in drive circuit

- Drives the IGBT under optimal conditions.

- The control IC of upper side arms have a built-in high voltage level shift circuit (HVIC).

- This IPM is possible for driven directly by a microprocessor. Of course, the upper side arm can also be driven directly. The voltage level of input signal is 3.3V or 5V.

- Since the wiring length between the internal drive circuit and IGBT is short and the impedance of the drive circuit is low, no reverse bias DC source is required.

- This IPM device requires four control power sources. One is a power supply for the lower side IGBTs and control ICs. The other three power supplies are power supplies for the upper side IGBTs with proper circuit isolation.

The IPM doesn't need insulated power supplies for the upper side drive because the IPM has a builtin bootstrap diodes (BSD).

Fig. 1-1 Block Diagram of Internal Circuit

1.2 Built-in protection circuits

- The following built-in protection circuits are incorporated in the IPM device:

- (OC): Over current protection

- (UV): Under voltage protection for power supplies of control IC

- (LT) or (OH): Temperature sensor output function or Overheating protection

- (FO): Fault alarm signal output

- The OC protection circuits protect the IGBT against over current, load short-circuit or arm short-circuit. The protection circuit monitors the emitter current using external shunt resistor in each lower side IGBT and thus it can protect the IGBT against arm short-circuit.

- The UV protection circuit is integrated into all of the IGBT drive circuits. This protection function is effective for a voltage drop of all of the high side drive circuits and the control power supply.

- The OH protection circuit protects the IPM from overheating. The OH protection circuit is built into the control IC of the lower side arm (LVIC).

- The temperature sensor output function enables to output measured temperature as an analog voltage (built in LVIC)

- The FO function outputs an fault signal, making it possible to shutdown the system reliably by outputting the fault signal to a micro processor unit which controls the IPM when the circuit detects abnormal conditions.

### 1.3 Compact package

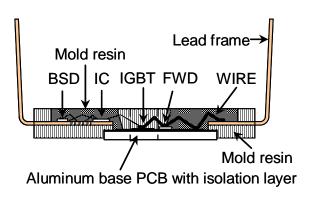

•The package of this product with an aluminum base, which further improves the heat radiation.

•The control input terminals have a shrink pitch of 1.778mm (70mil).

•The power terminals have a standard pitch of 2.54mm (100mil).

•The total dissipation loss has been improved by improvement of the trade-off between the Collector-Emitter saturation voltage Vce(sat) and switching loss.

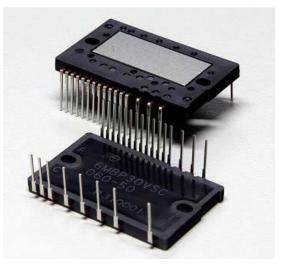

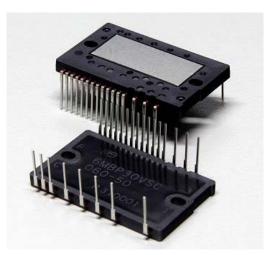

Fig.1-2 Package overview

Fig.1-3 Package cross section

### 2. Product line-up and applicable products for this manual

|                 |                                  |                | -                                        |                                      |                                                               |

|-----------------|----------------------------------|----------------|------------------------------------------|--------------------------------------|---------------------------------------------------------------|

|                 | Rating of IGBT Isolation Voltage |                |                                          |                                      |                                                               |

| Type name       | Voltage<br>[V]                   | Current<br>[A] | [Vrms]                                   | Variation                            | Target application                                            |

| 6MBP15VSG060-50 | 600                              | 15             | 1500Vrms<br>Sinusoidal 60Hz, 1min.       | LT <sup>*1</sup>                     | <ul> <li>Roof air conditioner<br/>compressor drive</li> </ul> |

| 6MBP15VSH060-50 |                                  |                | (Between shorted all terminals and case) | LT <sup>*1</sup>                     | <ul> <li>Heat pump<br/>applications</li> </ul>                |

|                 |                                  |                |                                          | OH <sup>*1</sup>                     | •Fan motor drive                                              |

| 6MBP20VSA060-50 |                                  | 20             |                                          | LT <sup>*1</sup>                     |                                                               |

| 6MBP20VSC060-50 |                                  |                |                                          | LT <sup>*1</sup>                     |                                                               |

|                 |                                  |                |                                          | OH <sup>*1</sup>                     |                                                               |

| 6MBP30VSA060-50 |                                  | 30             |                                          | LT <sup>*1</sup>                     |                                                               |

|                 |                                  |                |                                          | . <del></del>                        |                                                               |

| 6MBP30VSC060-50 |                                  |                |                                          | LT <sup>*1</sup><br>OH <sup>*1</sup> |                                                               |

|                 |                                  |                |                                          |                                      |                                                               |

Table. 1-1 Line-up

\*1 (LT): Temperature sensor output function (LT) (OH): Overheating protection function (OH)

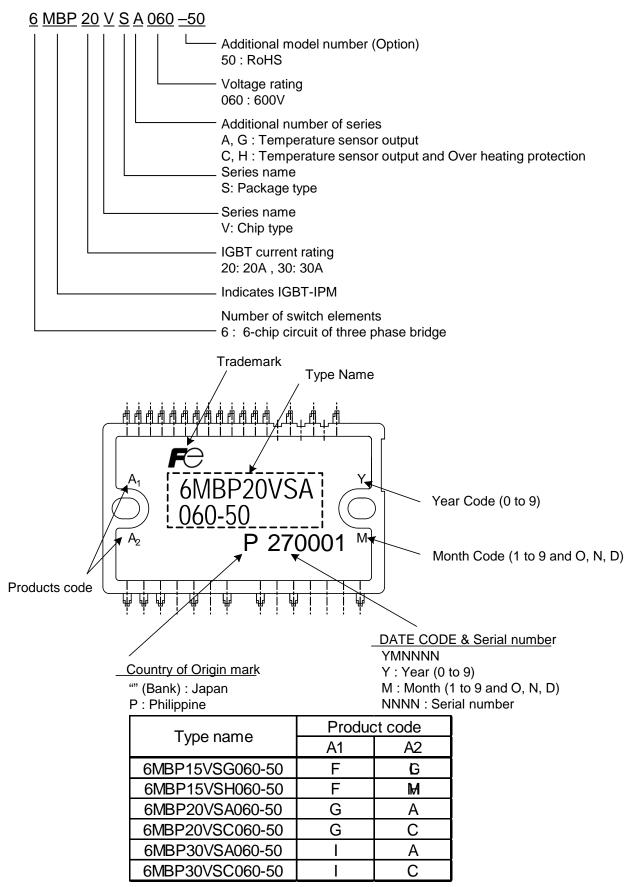

# 3. Definition of Type Name and Marking Spec.

• Type name

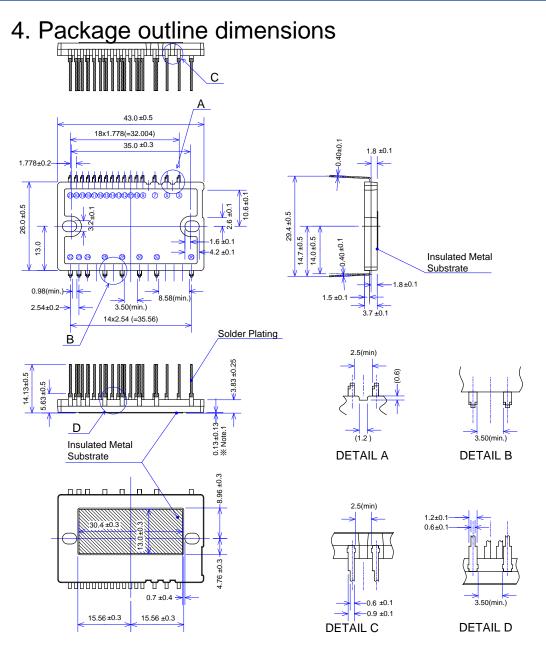

Fig.1-4 Marking Specification

Note.1

Unit: mm

The IMS (Insulated Metal Substrate) deliberately protruded from back surface of case. It is improved of thermal conductivity between IMS and heat-sink.

| Pin No. | Pin Name         | Pin N |

|---------|------------------|-------|

| 3       | VB(U)            | 22    |

| 5       | VB(V)            | 23    |

| 7       | VB(W)            | 24    |

| 9       | IN(HU)           | 26    |

| 10      | IN(HV)           | 28    |

| 11      | IN(HW)           | 30    |

| 12      | V <sub>CCH</sub> | 32    |

| 13      | COM              | 36    |

| 14      | IN(LU)           |       |

| 15      | IN(LV)           |       |

| 16      | IN(LW)           |       |

| 17      | V <sub>CCL</sub> |       |

| 18      | VFO              |       |

| 19      | IS               |       |

| 20      | COM              |       |

| 21      | Temp             |       |

| Pin No. | Pin Name |

|---------|----------|

| 22      | N(W)     |

| 23      | N(V)     |

| 24      | N(U)     |

| 26      | W        |

| 28      | V        |

| 30      | U        |

| 32      | Р        |

| 36      | NC       |

|         |          |

|         |          |

|         |          |

|         |          |

|         |          |

Fig.1-5. Case outline drawings

## 5. Absolute Maximum Ratings

An example of the absolute maximum ratings of 6MBP20VSA060-50 is shown in Table 1-2.

### Table 1-2 Absolute Maximum Ratings at Tj=25°C,Vcc=15V (unless otherwise specified)

| Item                                                | Symbol                                                                  | Rating                                                                            | Unit | Description                                                                                                                                 |

|-----------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| DC bus Voltage                                      | V <sub>DC</sub>                                                         | 450                                                                               | V    | DC voltage that can be applied between P-N(U),N(V),N(W) terminals                                                                           |

| Bus voltage (Surge)                                 | V <sub>DC(Surge)</sub>                                                  | 500                                                                               | V    | Peak value of the surge voltage that can be<br>applied between P-N(U),N(V),N(W)<br>terminals in switching                                   |

| Collector-Emitter Voltage                           | V <sub>CES</sub>                                                        | 600                                                                               | V    | Maximum collector-emitter voltage of the<br>built-in IGBT chip and repeated peak<br>reverse voltage of the FWD chip                         |

| Collector Current                                   | I <sub>C@25</sub>                                                       | 20                                                                                | A    | Maximum collector current for the IGBT chip<br>Tc=25°C, Tj=150°C                                                                            |

| Peak Collector Current                              | I <sub>CP@25</sub>                                                      | 60                                                                                | А    | Maximum pulse collector current for the IGBT chip Tc=25°C, Tj=150°C                                                                         |

| Diode Forward current                               | I <sub>F@25</sub>                                                       | 20                                                                                | А    | Maximum forward current for the FWD chip Tc=25°C, Tj=150°C                                                                                  |

| Peak Diode Forward current                          | I <sub>FP@25</sub>                                                      | 60                                                                                | А    | Maximum pulse forward current for the FWD chip Tc=25°C, Tj=150°C                                                                            |

| Collector Power Dissipation                         | P <sub>D_IGBT</sub>                                                     | 63.1                                                                              | W    | Maximum power dissipation for one IGBT element at Tc=25°C, Tj=150°C                                                                         |

| FWD Power Dissipation                               | P <sub>D_FWD</sub>                                                      | 30.6                                                                              | W    | Maximum power dissipation for one FWD element at Tc=25°C, Tj=150°C                                                                          |

| Maximum Junction Temperature of Inverter block      | Tj                                                                      | +150                                                                              | °C   | Maximum junction temperature of the IGBT chips and the FWD chips                                                                            |

| Operating Junction Temperature<br>of Inverter block | T <sub>jop</sub>                                                        | -40 ~ +125                                                                        | °C   | Junction temperature of the IGBT and FWD chips during continuous operation                                                                  |

| High-side Supply Voltage                            | V <sub>CCH</sub>                                                        | -0.5 ~ 20                                                                         | V    | Voltage that can be applied between COM and $V_{\mbox{\scriptsize CCH}}$ terminal                                                           |

| Low-side Supply Voltage                             | V <sub>CCL</sub>                                                        | -0.5 ~ 20                                                                         | V    | Voltage that can be applied between COM and $V_{\mbox{\scriptsize CCL}}$ terminal                                                           |

| High-side Bias Supply Voltage                       | VB <sub>(U)-COM</sub><br>VB <sub>(V)-COM</sub><br>VB <sub>(W)-COM</sub> | -0.5 ~ 620                                                                        | V    | Voltage that can be applied between VB(U) terminal and COM, VB(V) terminal and COM,VB(W) terminal and COM.                                  |

| High-side Bias Voltage for IGBT gate driving        | VB(U)<br>VB(V)<br>VB(W)                                                 | 20                                                                                | V    | Voltage that can be applied between U<br>terminal and VB(U) terminal , V terminal and<br>VB(V) terminal , W terminal and VB(W)<br>terminal. |

| Input Signal Voltage                                | V <sub>IN</sub>                                                         | $\begin{array}{l} -0.5 \sim V_{CCH} + 0.5 \\ -0.5 \sim V_{CCL} + 0.5 \end{array}$ | V    | Voltage that can be applied between COM and each Vin terminal                                                                               |

| Input Signal Current                                | I <sub>IN</sub>                                                         | 3                                                                                 | mA   | Maximum input current that flows from Vin terminal to COM                                                                                   |

| Fault Signal Voltage                                | V <sub>FO</sub>                                                         | $-0.5 \sim V_{CCL} + 0.5$ .                                                       | V    | Voltage that can be applied between COM and VFO terminal                                                                                    |

| Fault Signal Current                                | I <sub>FO</sub>                                                         | 1                                                                                 | mA   | Sink current that flows from VFO to COM terminal                                                                                            |

| Item                                                       | Symbol           | Rating                    | Unit | Descriptions                                                                                                                                                                |

|------------------------------------------------------------|------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Over Current sensing<br>Input Voltage                      | V <sub>IS</sub>  | $-0.5 \sim V_{CCL} + 0.5$ | V    | Voltage that can be applied between IS and COM terminal                                                                                                                     |

| Maximum Junction Temperature of Control circuit block      | Tj               | +150                      | °C   | Maximum junction temperature of the control circuit block                                                                                                                   |

| Operating Junction Temperature<br>of Control circuit block | T <sub>jop</sub> | -40 ~ +125                | °C   | Junction temperature of the control circuit block during continuous operation                                                                                               |

| Operating Case Temperature                                 | T <sub>C</sub>   | -40 ~ +125                | °C   | Operating case temperature (temperature of the aluminum plate directly under the IGBT or the FWD)                                                                           |

| Storage Temperature                                        | T <sub>stg</sub> | -40 ~ +125                | °C   | Range of ambient temperature for storage or transportation, when there is no electrical load                                                                                |

| Isolation Voltage                                          | Viso             | AC 1500                   | Vrms | Maximum effective value of the sine-wave<br>voltage between the terminals and the heat<br>sink, when all terminals are shorted<br>simultaneously. (Sine wave = 60Hz / 1min) |

.

•

.

•

| Table 1-2 Absolute Maximum Ratings at Tj=25°C,Vcc=15V | (Continued)  |

|-------------------------------------------------------|--------------|

|                                                       | (Containada) |

•

.

•

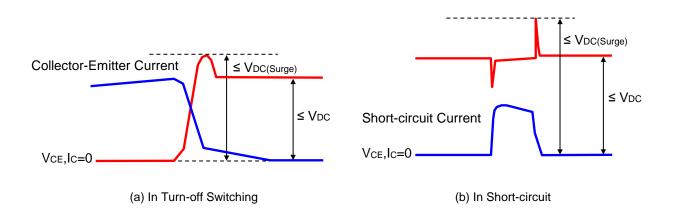

#### The Collector Emitter Voltages specified in absolute maximum rating

Regarding the absolute maximum rating of collector-emitter voltage of the IGBT is specified below.

During operation of the IPM, the voltage between P and N(\*) is usually applied to the one phase of upper or lower side IGBT. Therefore, the voltage applied between P and N(\*) must not exceed absolute maximum ratings of IGBT. The Collector-Emitter voltages specified in absolute maximum rating are described below.

N(\*): N(U),N(V),N(W)

- VCES :Absolute Maximum rating of IGBT Collector Emitter Voltage.

- V<sub>DC</sub> :DC bus voltage Applied between P and N(\*).

- V<sub>DC(Surge)</sub> :The total of DC bus voltage and surge voltage which generated by the wiring (or pattern) inductance from P-N(\*) terminal to the bulk capacitor.

Fig. 1-6 The Collector- Emitter voltages to be considered.

Fig. 1-6 shows an example waveforms of turn-off and short-circuit of the IPM. The  $V_{DC(surge)}$  is different in the each situation, therefore,  $V_{DC}$  should be set considering these situation.

$V_{CES}$  represents the absolute maximum rating of IGBT Collector-Emitter voltage. And  $V_{DC(Surge)}$  is specified considering the margin of the surge voltage which is generated by the wiring inductance in this IPM. Furthermore,  $V_{DC}$  is specified considering the margin of the surge voltage which is generated by the wiring (or pattern) stray inductance between the P-N(\*) terminal and the capacitor.

# Chapter 2

# Description of Terminal Symbols and Terminology

| Contents                           | Page |

|------------------------------------|------|

| 1. Description of Terminal Symbols | 2-2  |

| 2. Description of Terminology      | 2-3  |

# 1. Description of Terminal Symbols

Table 2-1 and 2-2 show the description of terminal symbols and terminology respectively.

| Table 2-1 | Description | of Termina | l Symbols |

|-----------|-------------|------------|-----------|

|           | Description |            |           |

| Pin No. | Pin Name         | Pin Description                                 |

|---------|------------------|-------------------------------------------------|

| 3       | VB(U)            | High side bias voltage for U-phase IGBT driving |

| 5       | VB(V)            | High side bias voltage for V-phase IGBT driving |

| 7       | VB(W)            | High side bias voltage for W-phase IGBT driving |

| 9       | IN(HU)           | Signal input for high side U-phase              |

| 10      | IN(HV)           | Signal input for high side V-phase              |

| 11      | IN(HW)           | Signal input for high side W-phase              |

| 12      | V <sub>CCH</sub> | High side control supply                        |

| 13      | СОМ              | Common supply ground                            |

| 14      | IN(LU)           | Signal input for low side U-phase               |

| 15      | IN(LV)           | Signal input for low side V-phase               |

| 16      | IN(LW)           | Signal input for low side W-phase               |

| 17      | V <sub>CCL</sub> | Low side control supply                         |

| 18      | VFO              | Fault output                                    |

| 19      | IS               | Over current sensing voltage input              |

| 20      | СОМ              | Common supply ground                            |

| 21      | TEMP             | Temperature sensor output                       |

| 22      | N(W)             | Negative bus voltage input for W-phase          |

| 23      | N(V)             | Negative bus voltage input for V-phase          |

| 24      | N(U)             | Negative bus voltage input for U-phase          |

| 26      | W                | Motor W-phase output                            |

| 28      | V                | Motor V-phase output                            |

| 30      | U                | Motor U-phase output                            |

|         |                  | Desitive hus voltage input                      |

| 32      | Р                | Positive bus voltage input                      |

# 2. Description of Terminology

Table 2-2 Description of Terminology

| (1) Inverter block                     | 140                  | re 2-2 Description of Terminology                                                                                                                                                       |

|----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item                                   | Symbol               | Description                                                                                                                                                                             |

| Zero gate Voltage Collector<br>current | I <sub>CES</sub>     | Collector current when a specified voltage is applied between the collector and emitter of an IGBT with all input signals L (=0V) $$                                                    |

| Collector-emitter saturation voltage   | V <sub>CE(sat)</sub> | Collector-emitter voltage at a specified collector current when the input signal of only the element to be measured is H (= $5V$ ) and the inputs of all other elements are L (= $0V$ ) |

| FWD<br>forward voltage drop            | V <sub>F</sub>       | Forward voltage at a specified forward current with all input signals L (=0V)                                                                                                           |

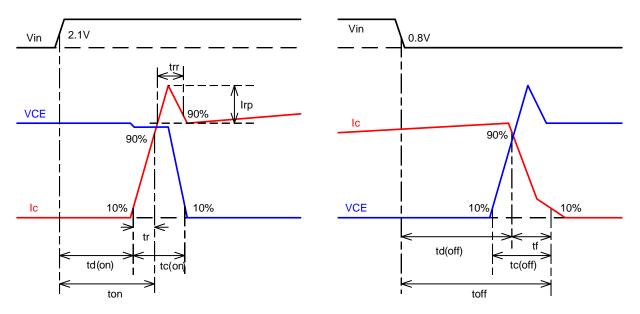

| Turn-on time                           | ton                  | The time from the input signal rising above the threshold value until the collector current becomes 90% of the rating. See Fig. 2-1.                                                    |

| Turn-on delay                          | td(on)               | The time from the input signal rising above the threshold value until the collector current decreases to 10% of the rating. See Fig. 2-1.                                               |

| Turn-on rise time                      | tr                   | The time from the collector current becoming 10% at the time of IGBT turn-on until the collector current becomes 90%. See Fig. 2-1.                                                     |

| VCE-IC Cross time of turn-on           | tc(on)               | The time from the collector current becoming 10% at the time of IGBT turn on until the VCE voltage of IGBT dropping below 10% of the rating. See Fig. 2-1.                              |

| Turn-off time                          | toff                 | The time from the input signal dropping below the threshold value until the VCE voltage of IGBT becomes 90% of the rating. See Fig. 2-1.                                                |

| Turn-off delay                         | td(off)              | The time from the input signal dropping below the threshold value until the collector current decreases to 90%. See Fig. 2-1.                                                           |

| Turn-on fall time                      | tf                   | The time from the collector current becoming 90% at the time of IGBT turn-off until the collector current decreases to 10%. See Fig. 2-1.                                               |

| VCE-IC Cross time of turn-off          | tc(off)              | The time from the VCE voltage becoming 10% at the time of IGBT turn ff until the collector current dropping below 10% of the rating. See Fig. 2-1.                                      |

| FWD<br>Reverse recovery time           | trr                  | The time required for the reverse recovery current of the built-in diode to disappear. See Fig. 2-1.                                                                                    |

### (2) Control circuit block

| Item                                         | Symbol               | Description                                                                                                                     |

|----------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Circuit current of<br>Low-side drive IC      | I <sub>CCL</sub>     | Current flowing between control power supply $V_{\text{CCL}}$ and COM                                                           |

| Circuit current of<br>High-side drive IC     | I <sub>ссн</sub>     | Current flowing between control power supply $V_{\mbox{\scriptsize CCH}}$ and COM                                               |

| Circuit current of Bootstrap circuit         | I <sub>ССНВ</sub>    | Current flowing between upper side IGBT bias voltage supply VB(U) and U,VB(V) and V or VB(W) and W on the P-side (per one unit) |

| Input Signal threshold                       | Vth(on)              | Control signal voltage when IGBT changes from OFF to ON                                                                         |

| voltage                                      | Vth(off)             | Control signal voltage when IGBT changes from ON to OFF                                                                         |

| Input Signal threshold<br>hysteresis voltage | Vth(hys)             | The hysteresis voltage between Vth(on) and Vth(off).                                                                            |

| Operational input pulse width                | t <sub>IN(on)</sub>  | Control signal pulse width necessary to change IGBT from OFF to ON.<br>Refer Chapter 3 section 4.                               |

| Operational input pulse width                | t <sub>IN(off)</sub> | Control signal pulse width necessary to change IGBT from ON to OFF.<br>Refer Chapter 3 section 4.                               |

### Chapter 2 Description of Terminal Symbols and Terminology

### Table 2-2 Description of Terminology

| (2) Control circuit block (0                  | ,                     |                                                                                                                                                                                                                                    |

|-----------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item                                          | Symbol                | Description                                                                                                                                                                                                                        |

| Input current                                 | l <sub>in</sub>       | Current flowing between signal input IN(HU,HV,HW,LU,LV,LW) and COM.                                                                                                                                                                |

| Input pull-down resistance                    | R <sub>IN</sub>       | Input resistance of resister in input terminals IN(HU,HV,HW,LU,LV,LW).<br>They are inserted between each input terminal and COM.                                                                                                   |

| Foult output veltage                          | V <sub>FO</sub> (H)   | Output voltage level of VFO terminal under the normal operation (The lower side arm protection function is not actuated.) with pull-up resister $10k\Omega$ .                                                                      |

| Fault output voltage                          | V <sub>FO</sub> (L)   | Output voltage level of VFO terminal after the lower side arm protection function is actuated.                                                                                                                                     |

| Fault output pulse width                      | t <sub>FO</sub>       | Period in which an fault status continues to be output (VFO) from the VFO terminal after the lower side arm protection function is actuated. Refer chapter 3 section 6.                                                            |

| Over current protection voltage level         | V <sub>IS</sub> (ref) | Threshold voltage of IS terminal at the over current protection.<br>Refer chapter 3 section 5.                                                                                                                                     |

| Over Current Protection<br>Trip delay time    | td <sub>(IS)</sub>    | The time from the Over current protection triggered until the collector current becomes 50% of the rating. Refer chapter 3 section 5.                                                                                              |

| Output Voltage of temperature sensor          | V(temp)               | The output voltage of temp. It is applied to the temperature sensor output model. Refer chapter 3 section 7.                                                                                                                       |

| Overheating protection temperature            | ТОН                   | Tripping temperature of over heating. The temperature is observed by LVIC.<br>All low side IGBTs are shut down when the LVIC temperature exceeds overheating<br>threshold. See Fig.2-2 and refer chapter 3 section 8.              |

| Overheating protection hysteresis             | TOH(hys)              | Hysteresis temperature required for output stop resetting after protection operation.<br>See Fig.2-2 and refer chapter 3 section 8.<br>TOH and TOH(hys) are applied to the overheating protection model.                           |

| Vcc Under voltage trip level of Low-side      | V <sub>CCL(OFF)</sub> | Tripping voltage in under voltage of the Low-side control IC power supply.<br>All low side IGBTs are shut down when the voltage of $V_{CCL}$ drops below this threshold.<br>Refer chapter 3 section 1.                             |

| Vcc Under voltage reset level<br>of Low-side  | V <sub>CCL(ON)</sub>  | Resetting threshold voltage from under voltage trip status of VCCL.<br>Refer chapter 3 section 1.                                                                                                                                  |

| Vcc Under voltage hysteresis of Low-side      | V <sub>CCL(hys)</sub> | Hysteresis voltage between $V_{\text{CCL}(\text{OFF})}$ and $V_{\text{CCL}(\text{ON})}.$                                                                                                                                           |

| Vcc Under voltage trip level of High-side     | V <sub>CCH(OFF)</sub> | Tripping voltage in under voltage of High-side control IC power supply.<br>The IGBTs of high-side are shut down when the voltage of VCCH drops below this<br>threshold. Refer chapter 3 section 1.                                 |

| Vcc Under voltage reset level<br>of High-side | V <sub>CCH(ON)</sub>  | Resetting threshold voltage from under voltage trip status of VCCH. See Fig.3-3<br>Resetting voltage at which the IGBT performs shutdown when the High-side control<br>power supply voltage VCCH drops. Refer chapter 3 section 1. |

| Vcc Under voltage hysteresis of High-side     | V <sub>CCH(hys)</sub> | Hysteresis voltage between $V_{CCH(OFF)}$ and $V_{CCH(ON)}$ .                                                                                                                                                                      |

| VB Under voltage trip level                   | V <sub>B(OFF)</sub>   | Tripping voltage in under voltage of VB(*). The IGBTs of high-side are shut down when the voltage of VB(*) drops below this threshold. Refer chapter 3 section 2.                                                                  |

| VB Under voltage reset level                  | V <sub>B(ON)</sub>    | Resetting voltage at which the IGBT performs shutdown when the upper side arm IGBT bias voltage VB(*) drops. Refer chapter 3 section 2.                                                                                            |

| VB Under voltage hysteresis                   | V <sub>B(hys)</sub>   | Hysteresis voltage between $V_{B(OFF)}$ and $V_{B(ON)}$ .                                                                                                                                                                          |

### (2) Control circuit block (Continued)

### Table 2-2 Description of Terminology

| (3) | BSD | block |

|-----|-----|-------|

|-----|-----|-------|

| Item                                  | Symbol              | Description                                         |

|---------------------------------------|---------------------|-----------------------------------------------------|

| Forward voltage of<br>Bootstrap diode | V <sub>F(BSD)</sub> | BSD Forward voltage at a specified forward current. |

### (4) Thermal Characteristics

| Item                                                        | Symbol                    | Description                                                                                                                         |

|-------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Junction to Case Thermal<br>Resistance<br>(per single IGBT) | Rth(j-c)_ <sub>IGBT</sub> | Thermal resistance from the junction to the case of single IGBT.                                                                    |

| Junction to Case Thermal<br>Resistance<br>(per single FWD)  | Rth(j-c)_ <sub>FWD</sub>  | Thermal resistance from the junction to the case of single FWD.                                                                     |

| Case to Heat sink<br>Thermal Resistance                     | Rth(c-f)                  | Thermal resistance between the case and heat sink, when mounted on a heat sink at the recommended torque using the thermal compound |

### (5) Mechanical Characteristics

| Item                    | Symbol | Description                                                                  |

|-------------------------|--------|------------------------------------------------------------------------------|

| Tighten torque          | -      | Screwing torque when mounting the IPM to a heat sink with a specified screw. |

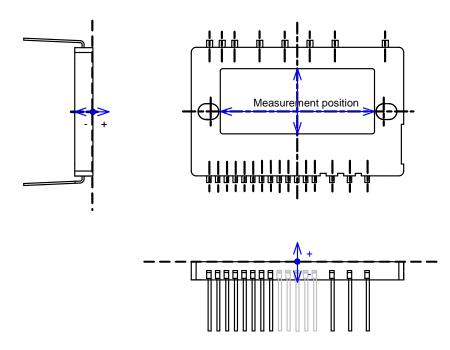

| Heat-sink side flatness | -      | Flatness of a heat sink side. See Fig.2-3.                                   |

Fig.2-1 Switching waveforms

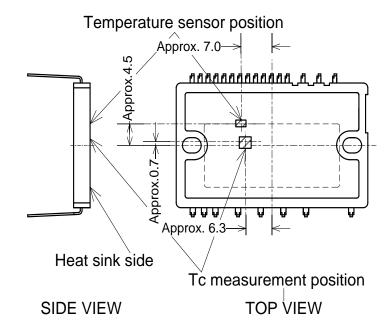

Fig.2-2 The measurement position of temperature sensor and Tc.

Fig.2-3 The measurement point of heat-sink side flatness.

# Chapter 3

# **Detail of Signal Input/Output Terminals**

| Contents                                          | Page |

|---------------------------------------------------|------|

| 1. Control Power Supply Terminals Vссн, VссL, COM | 3-2  |

| 2. Power Supply Terminals of High Side VB(U,V,W)  | 3-6  |

| 3. Function of Internal BSDs (Boot Strap Diodes)  | 3-9  |

| 4. Input Terminals IN(HU,HV,HW), IN(LU,LV,LW)     | 3-13 |

| 5. Over Current Protection Input Terminal IS      | 3-16 |

| 6. Fault Status Output Terminal VFO               | 3-17 |

| 7. Temperature Sensor Output Terminal TEMP        | 3-18 |

| 8. Over Heat Protection                           | 3-20 |

# 1. Control Power Supply Terminals VCCH, VCCL, COM

1. Voltage Range of control power supply terminals VCCH, VCCL

Please connect a single 15Vdc power supply between VCCH,VCCL and COM terminals for the IPM control power supply. The voltage should be regulated to  $15V \pm 10\%$  for proper operation. Table 3-1 describes the behavior of the IPM for various control supply voltages. A low impedance capacitor and a high frequency decoupling capacitor should be connected close to the terminals of the power supply.

High frequency noise on the power supply might cause a malfunction of the internal control IC or erroneous fault signal output. To avoid these problems, the maximum amplitude of voltage ripple on the power supply should be less than  $\pm 1V/\mu$ s.

The potential at the COM terminal is different from that at the  $N(*)^{*1}$  power terminal. It is very important that all control circuits and power supplies are referred to the COM terminal and not to the  $N(*)^{*1}$  terminals. If circuits are improperly connected, an additional current might flow through the sense resistor and it cause an improper operation of the short-circuit protection function. In general, it is best practice to make the COM as the ground in the PCB layout.

The main control power supply is also connected to the bootstrap circuit which provide a power to floating supplies for the high side gate drivers.

When high side control supply voltage (VCCH and COM) falls down under VCCH UV (Under Voltage protection) level, only the IGBT which occurred the under voltage condition becomes off-state even though the input signal is ON condition.

When low side control supply voltage (VccL and COM) falls down under VccL UV level, all lower side IGBTs become off-state even though the input signal is ON condition.

| Control Voltage Range [V] | Function Operations                                                                                                                                                                                                                                                                                                                        |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 ~ 4                     | The IPM doesn't work. UV and fault output are not activated. dV/dt noise on the main P-N supply might cause a malfunction of the IGBTs.                                                                                                                                                                                                    |

| 4 ~ 13                    | The IPM start to work. UV is activated, control input signals are blocked and a fault output VFO is generated.                                                                                                                                                                                                                             |

| 13 ~ 13.5                 | UV is reset. IGBTs are operated in accordance with the control gate input. Driving voltage is below the recommended range, so $V_{CE(sat)}$ and the switching loss will be larger than that under normal condition and high side IGBTs can't operate after VB(*) <sup>*2</sup> initial charging because VB(*) can't reach to $V_{B(ON)}$ . |

| 13.5 ~ 16.5               | Normal operation. This is the recommended operating condition.                                                                                                                                                                                                                                                                             |

| 16.5 ~ 20                 | The lower side IGBTs are still operated. Because driving voltage is above<br>the recommended range, IGBT's switching is faster. It causes increasing<br>system noise. And peak short circuit current might be too large for proper<br>operation of the short circuit protection.                                                           |

| Over 20                   | Control circuit in this IPM might be damaged.<br>If necessary, it is recommended to insert a zener-diode between each pair<br>of control supply terminals.                                                                                                                                                                                 |

\*1 N(\*) : N(U), N(V), N(W)

\*2 VB(\*) : VB(U)-U, VB(V)-V,VB(W)-W

2. Under Voltage protection of control power supply terminals VCCH, VCCL

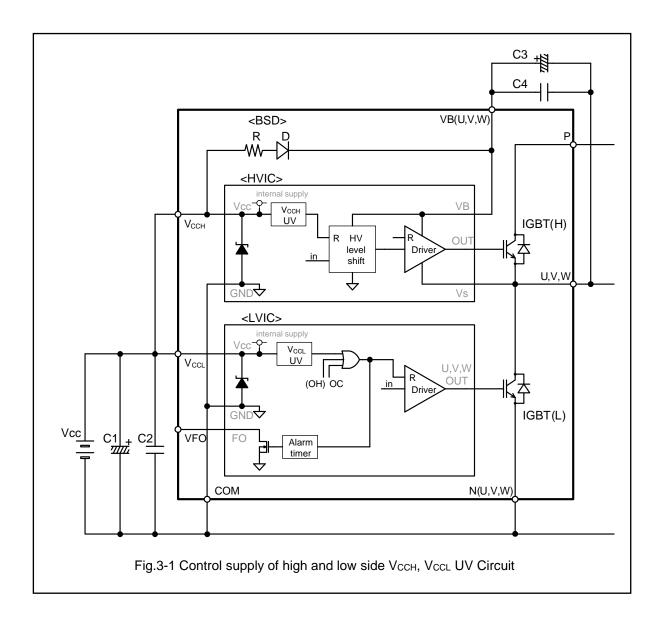

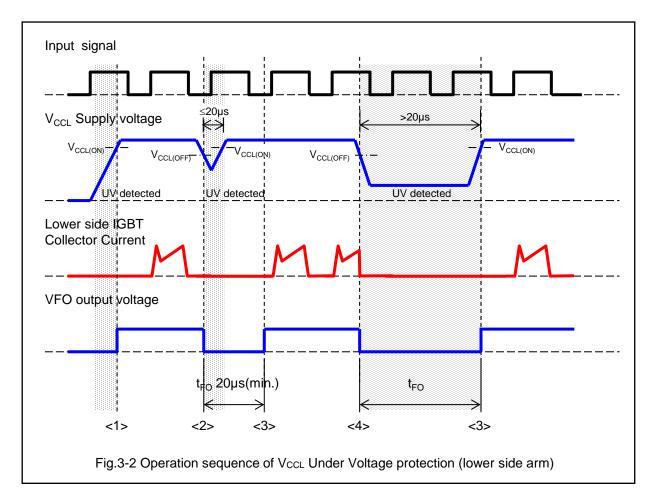

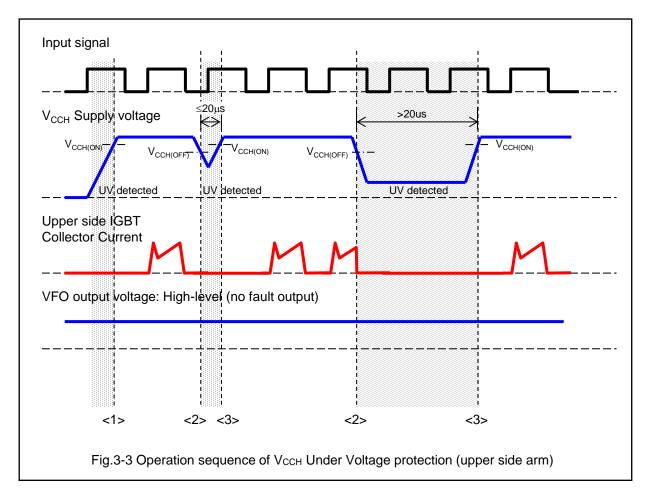

Fig.3-1 shows the UV protection circuit of high side and low side control supply(VCCH,VCCL). Fig.3-2 and Fig.3-3 shows the sequence of UV operation of VCCH and VCCL.

As shown in Fig.3-1, a diode is electrically connected to the  $V_{CCH}$ ,  $V_{CCL}$  and COM terminals. The diode should not be used for a voltage clamp intentionally otherwise the IPM might be damaged.

- <1> When VccL is lower than VccL(ON), all lower side IGBTs are OFF state. After VccL exceeding VccL(ON), the fault output VFO is released (high level). And the LVIC starts to operate, then next input is activated.

- <2> The fault output VFO is activated when VccL falls below VccL(OFF), and all lower side IGBT remains OFF state.

If the voltage drop time is less than  $20\mu s$ , the minimum pulse width of the fault output signal is  $20\mu s$  and all lower side IGBTs are OFF state regardless of the input signal condition.

- <3> UV is reset after t<sub>FO</sub> and V<sub>CCL</sub> exceeding V<sub>CCL(ON)</sub>, then the fault output VFO is reset simultaneously. After that the LVIC starts to operate from the next input signal.

- <4> When the voltage drop time is more than t<sub>FO</sub>, the fault output pulse width is generated and all lower side IGBTs are OFF state regardless of the input signal condition during the same time.

- <1> When VccH is lower than VccH(ON), the upper side IGBT is OFF state. After VccH exceeds VccH(ON), the HVIC starts to operate from the next input signals. The fault output VFO is constant (high level) regardless VccH.

- <2> After VCCH falls below VCCH(OFF), the upper side IGBT remains OFF state. But the fault output VFO keeps high level.

- <3> The HVIC starts to operate from the next input signal after UV is reset.

# 2. Power Supply Terminals of High Side VB(U,V,W)

1. Voltage Range of high side bias voltage for IGBT driving terminals VB(U,V,W)

The VB(\*) voltage, which is the voltage difference between VB(U,V,W) and U,V,W, provides the supply to the HVICs within the IPM. This supply must be in the range of  $13.0 \sim 18.5$ V to ensure that the HVICs can fully drive the upper side IGBTs. The IPM includes UV function for the VB(\*) to ensure that the HVICs do not drive the upper side IGBTs, if the VB(\*) voltage drops below a specified voltage (refer to the datasheet). This function prevents the IGBT from operating in a high dissipation mode. Please note here, that the UV (under voltage protection) function of any high side section acts only on the triggered channel without any feedback to the control level.

In case of using bootstrap circuit, the IGBT drive power supply for upper side arms can be composed of one common power supply with a lower side arm. In the conventional IPM, three independent insulated power supplies were necessary for IGBT drive circuit of upper side arm.

The power supply of the upper side arm is charged when the lower side IGBT is turned on or freewheel current flows the lower side IGBT. Table 3-2 describes the behavior of the IPM for various control supply voltages. The control supply should be well filtered with a low impedance capacitor and a high frequency decoupling capacitor connected close to the terminals in order to prevent a malfunction of the internal control IC caused by a high frequency noise on the power supply.

When control supply voltage (VB(U)-U,VB(V)-V and VB(W)-W) falls down under UV (Under Voltage protection) level, only triggered phase IGBT is off-state regardless the input signal condition.

| Control Voltage Range [V] | The IPM function operations                                                                                                                                                                                                                                                     |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 ~ 4                     | HVICs are not activated. UV does not operate. dV/dt noise on the main P-<br>N supply might trigger the IGBTs.                                                                                                                                                                   |

| 4 ~ 12.5                  | HVICs start to operate. As the UV is activated, control input signals are blocked.                                                                                                                                                                                              |

| 12.5 ~ 13                 | UV is reset. The upper side IGBTs are operated in accordance with the control gate input. Driving voltage is below the recommended range, so $V_{CE(sat)}$ and the switching loss will be larger than that under normal condition.                                              |

| 13 ~ 18.5                 | Normal operation. This is the recommended operating condition.                                                                                                                                                                                                                  |

| 18.5 ~ 20                 | The upper side IGBTs are still operated. Because driving voltage is above<br>the recommended rage, IGBT's switching is faster. It causes increasing<br>system noise. And peak short circuit current might be too large for proper<br>operation of the short circuit protection. |

| Over 20                   | Control circuit in the IPM might be damaged. It is recommended to insert a zener-diode between each pair of high side power supply terminals.                                                                                                                                   |

Table 3-2 Functions versus high side bias voltage for IGBT driving VB(\*)

### 2. Under Voltage protection of high side power supply terminals VB(U,V,W)

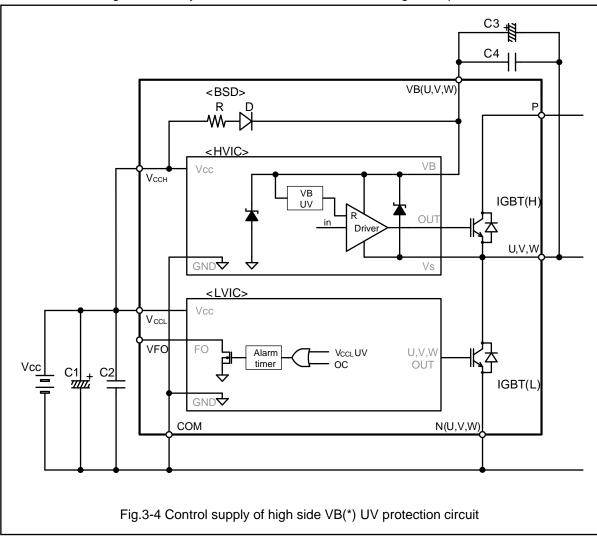

Fig.3-4 shows of high side (VB(U)-U,VB(V)-V and VB(W)-W) UV (Under Voltage protection) circuit block of the control power supply.

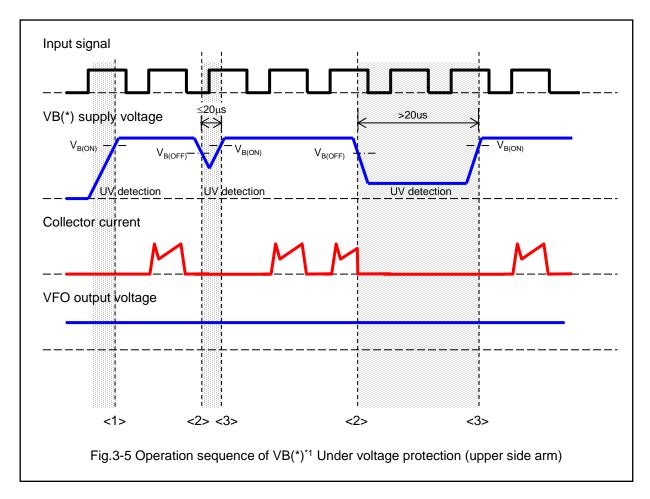

Fig.3-5 shows operation sequence of VB(U)-U,VB(V)-V,VB(W)-W Under Voltage operation.

As shown in Fig.3-4, diodes are electrically connected to the VB(U,V,W), U,V,W and COM terminals. These diodes protect the IPM from an input surge voltage. Don't use these diodes for a voltage clamp because the IPM might be destroyed if the diodes are used as a voltage clamp.

- <1> When VB(\*) is under V<sub>B(ON)</sub>, the upper side IGBT is OFF state. After VB(\*) exceeds V<sub>B(ON)</sub>, the HVIC starts to operate from the next input signal. The fault output VFO is constant (high level) regardless VB(\*).

- <2> After VB(\*) falls below  $V_{B(OFF)}$ , the upper side IGBT remains OFF state. But the fault output VFO keeps high level.

- <3> The HVIC starts to operate from the next input signal after UV is reset.

- \*1 VB(\*): VB(U)-U,VB(V)-V,VB(W)-W

# 3. Function of Internal BSDs (bootstrap Diodes)

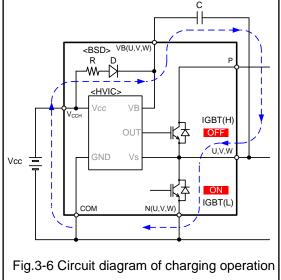

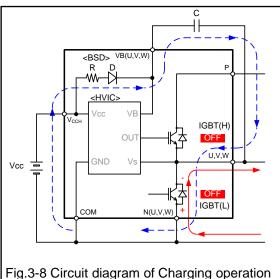

There are several ways in which the VB(\*)<sup>\*1</sup> floating supply can be generated. Bootstrap method is described here. The boot strap method is a simple and cheap solution. However, the duty cycle and on-time are limited by the requirement to refresh the charge in the bootstrap capacitor. As show in the Fig. 3-6, Fig. 3-8 and Fig. 3-11, the boot strap circuit consists of bootstrap diode and resistor whish are integrated in the IPM and an external capacitor.

1.Chargin and Discharging of Bootstrap Capacitor During Inverter Operation

a) Charging operation timing chart of bootstrap capacitor (C)

<Sequence (Fig.3-7) : lower side IGBT is turned on in Fig.3-6>

When lower side IGBT is ON state, the charging voltage on the bootstrap capacitance Vc(t1) is calculated by the following equations.

$VC(t1) = V_{CC}-V_{F}-V_{CE(sat)}-Ib\cdot R$  ..... Transient state  $VC(t1) \approx V_{CC}$  ..... Steady state

$\begin{array}{l} V_{F}: Forward \ voltage \ of \ Boost \ strap \ diode \ (D) \\ V_{CE(sat)}: \ Saturation \ voltage \ of \ lower \ side \ IGBT \\ R: \ Bootstrap \ resistance \ for \ inrush \ current \ limitation \ (R) \\ lb: \ Charge \ current \ of \ bootstrap \\ \end{array}$

When lower side IGBT is turned off, then the motor current flows through the free-wheel path of the upper side FWD. Once the electric potential of VS rises near to that of P terminal, the charging of C is stopped, and the voltage of C gradually declines due to a current consumed by the drive circuit.

# Gate signal of Upper side IGBT Gate signal of Lower side IGBT Voltage level of bootstrap capacitor Vs Fig.3-7 Timing chart of Charging operation

### \*1 VB(\*) : VB(U)-U,VB(V)-V,VB(W)-W

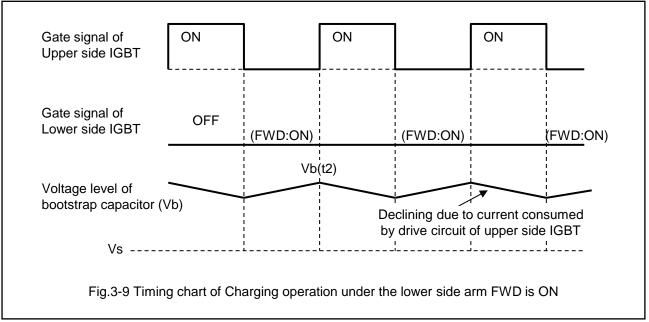

<Sequence (Fig.3-9): Lower side IGBT is OFF and Lower side FWD is ON (Freewheel current flows) in Fig.3-8 >

When the lower side IGBT is OFF and the lower side FWD is ON, a free wheeling current flows the lower side FWD. The voltage on the bootstrap capacitance Vc(t2) is calculated by the following equations:

$$\label{eq:Vc(t2)} \begin{split} &Vc(t2) = V_{CC} {-} V_{F} {+} V_{F(FWD)} {-} Ib {\cdot} R \; \dots . Transient \; state \\ &Vc(t2) \approx V_{CC} \; \qquad \dots . Steady \; state \end{split}$$

$V_F$  : Forward voltage of Boost strap diode (D)  $V_{F(FWD)}$  : Forward voltage of lower side FWD

R : Bootstrap resistance for inrush current limitation (R) Ib : Charge current of bootstrap

When both the lower side IGBT and the upper side IGBT are OFF, a regenerative current flows continuously through the freewheel path of the lower side FWD. Therefore the potential of V<sub>S</sub> drops to  $-V_F$ , then the bootstrap capacitor is re-charged to restore the declined potential. When the upper side IGBT is turned ON and the potential of V<sub>S</sub> exceeds Vcc, the charging of the bootstrap capacitor stops and the voltage on the bootstrap capacitor gradually declines due to consumption of the stored energy by the drive circuit.

under the lower side arm FWD is ON

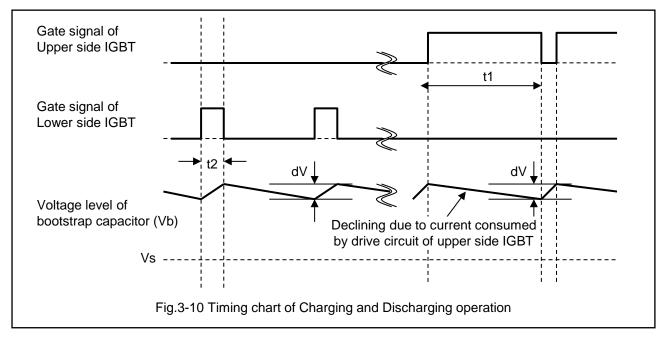

### 2) Setting the bootstrap capacitance and minimum ON/OFF pulse width

The parameter of bootstrap capacitor can be calculated by the following equation:

$$C = Ib \cdot \frac{t1}{dV}$$

\* t1 : the maximum ON pulse width of the upper side IGBT

- \* Ib : the drive current of the HVIC (depends on temperature and frequency characteristics)

- \* dV: the allowable discharge voltage. (see Fig.3-10)

A certain margin should be added to the calculated capacitance. The bootstrap capacitance is generally selected as large as 2~3 times of the calculated value.

The recommended minimum ON pulse width (t2) of the lower side IGBT should be basically determined such that the time constant  $C \cdot R$  will enable the discharged voltage (V) to be fully charged again during the ON period.

However, if only upper side IGBT has an ON-OFF-ON control mode (Sequence Fig.3-10), the time constant should be set so that the consumed energy during the ON period can be charged during the OFF period.

The minimum pulse width is decided by the minimum ON pulse width of the lower side IGBT or the minimum OFF pulse width of the upper side IGBT, whichever is shorter.

$$t_2 \ge \frac{R \cdot C \cdot dV}{Vcc - Vb_{(\min)}}$$

\* R : Series resistance of Bootstrap diode  $\Delta RF(BSD)$

\* C : Bootstrap capacitance

\* dV: the allowable discharge voltage.

\*Vcc : Voltage of HVICs and LVIC power supply (ex.15V)

\*Vb(min) : the minimum voltage of the upper side IGBT drive (Added margin to UV. ex. 14V)

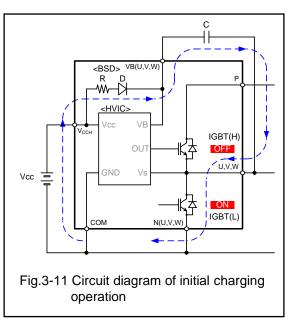

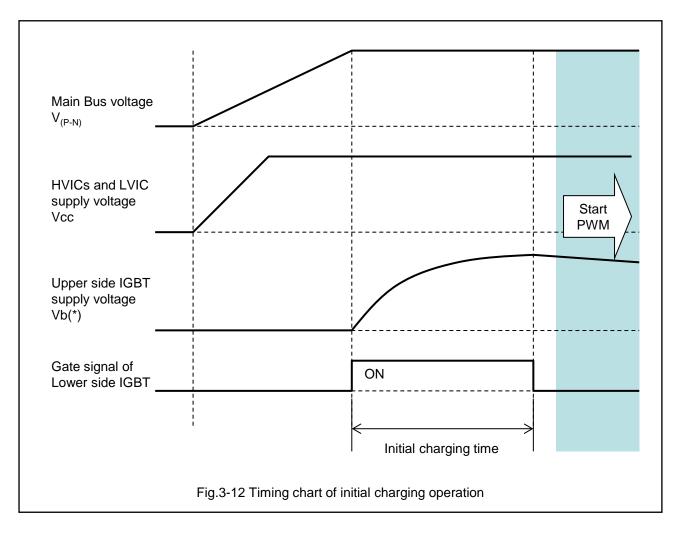

3) Setting the bootstrap capacitance for Initial charging

The initial charge of the bootstrap capacitor is required to start-up the inverter.

The pulse width or pulse number should be large enough to make a full charge of the bootstrap capacitor.

For reference, the charging time of  $10\mu$ F capacitor through the internal bootstrap diode is about 2ms.

# 4. Input Terminals IN(HU,HV,HW), IN(LU,LV,LW)

1. Input terminals Connection

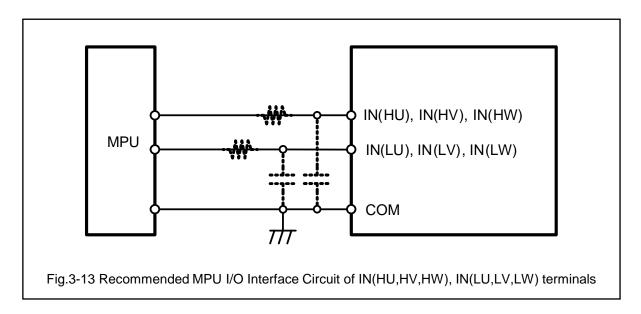

Fig.3-13 shows the input interface circuit between the MPU and the IPM. It is possible that the input terminals connect directly to the MPU. It should not need the external pull up and down resistors connected to the input terminals, input logic is active high and the pull down resistors are built in.

The RC coupling at each input (parts shown dotted in Fig.3-13) might change depending on the PWM control scheme used in the application and the wiring impedance of the application's PCB layout.

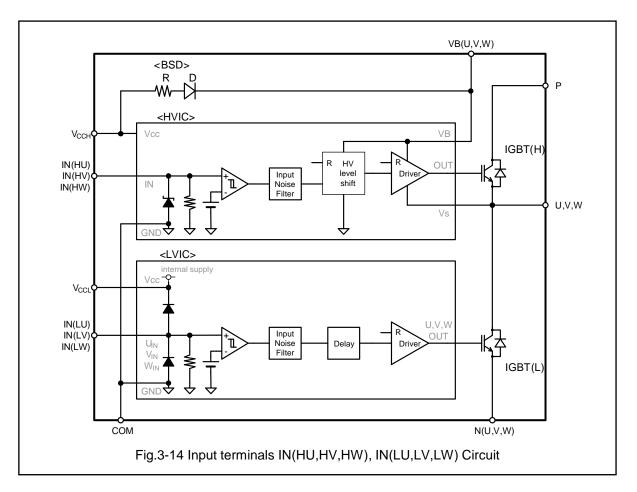

#### 2. Input terminal circuit

The input logic of this IPM is active high. This logic has removed the sequence restriction between the control supply and the input signal during startup or shutdown operation. Therefore it makes the system failsafe. In addition, the pull down resistors are built in to each input terminals in Fig.3-14. Thus, external pull-down resistors are not needed reducing the required external component. Furthermore, a direct connection to 3.3V-class MPU by the low input signal threshold voltage.

As shown in Fig.3-14, the input circuit integrates a pull-down resistor. Therefore, when using an external filtering resistor between the MPU output and input of the IPM, please care to the signal voltage drop at the input terminals to satisfy the turn-on threshold voltage requirement. For instance, R=100 $\Omega$  and C=1000pF for the parts shown dotted in Fig.3-13.

Fig.3-14 shows that the internal diodes are electrically connected to the  $V_{CCL}$ , IN(HU, HV, HW, LU, LV, LW) and COM terminals. They should not be used for the voltage clamp intentionally to prevent major problems and destroy the IPM.

#### 3. IGBT drive state versus Control signal pulse width

t<sub>IN(ON)</sub> is a recommended minimum turn-on pulse width for changing the IGBT state from OFF to ON, and t<sub>IN(OFF)</sub> is a recommended minimum turn-off pulse width for changing the IGBT state from ON to OFF. Fig.3-15 and Fig.3-16 show IGBT drive state for various control signal pulse width.

- state A : IGBT may turn on occasionally, even when the ON pulse width of control signal is less than minimum t<sub>IN(ON)</sub>. Also if the ON pulse width of control signal is less than minimum t<sub>IN(ON)</sub> and voltage is applied below -5V between U-COM,V-COM,W-COM , it may not turn off by the malfunction of the control circuit.

- state B: IGBT can turn on and is saturated under normal condition.

- state C : IGBT may turn on occasionally, even when the ON pulse width of control signal is less than minimum t<sub>IN(OFF)</sub>. Also if the OFF pulse width of control signal is less than minimum t<sub>IN(OFF)</sub> and voltage is applied below -5V between U-COM, V-COM, W-COM, it may not turn on by the malfunction of the control circuit.

- state D : IGBT can turn fully off under normal condition.

| Out recommended                                                                                         | Recommended range                                                                          |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| A                                                                                                       | В                                                                                          |  |

| לי איז איז איז איז איז איז איז איז איז אי                                                               |                                                                                            |  |

| Out recommended                                                                                         | Recommended range                                                                          |  |

| С                                                                                                       | D                                                                                          |  |

| 0 Minimum<br>t <sub>IN(OFF)</sub><br>Fig 3-16 IGBT drive state versus OFE pulse width of Control signal |                                                                                            |  |

| tiN(c<br>Fig.3-15 IGB<br>Out recommended<br>← range<br>C<br>0 Minin<br>tiN(c                            | T drive state versus ON pulse width of Control signal          Recommended range         D |  |

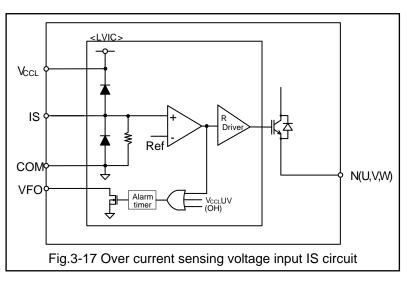

# 5. Over Current Protection Input Terminal IS

Over current protection (OC) is a function of detecting the IS voltage determined with the external shunt resistor, connected to  $N(^*)^{^{*1}}$  and COM.

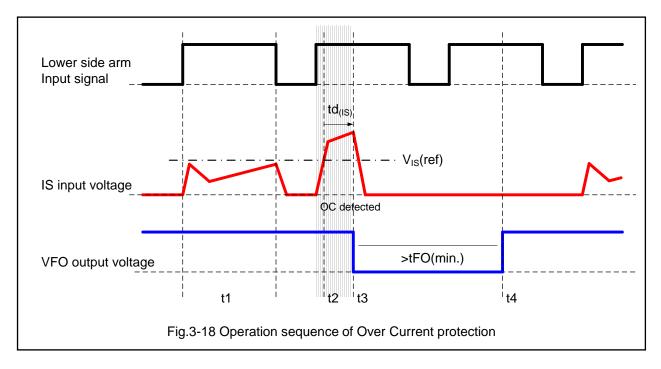

Fig.3-17 shows the over current sensing voltage input IS circuit block, and Fig.3-18 shows the OC operation sequence.

To prevent the IPM erroneous from the normal switching noise or recovery current, it is necessary to set an external R-C filter (time constant is approximately 1.5µs) to the IS terminal. Also the IPM and the shunt resistor should be wired as short as possible.

Fig.3-17 shows that the diodes in the IPM are electrically connected to the V<sub>CCL</sub>, IS and COM terminals. They should not be used for the voltage clamp intentionally to prevent major problems and destroy the IPM.

\*1 N(\*) : N(U), N(V), N(W)

- t1 : IS input voltage does not exceed V<sub>IS</sub>(ref), while the collector current of the lower side IGBT is under the normal operation.

- t2 : When IS input voltage exceeds  $V_{IS}(ref)$ , the OC is detected.

- t3 : The fault output VFO is activated and all lower side IGBT shut down simultaneously after the over current protection delay time  $td_{(IS)}$ . Inherently there is dead time of LVIC in  $td_{(IS)}$ .

- t4 : After the fault output pulse width tFO, the OC is reset. Then next input signal is activated.

# 6. Fault Status Output Terminal VFO

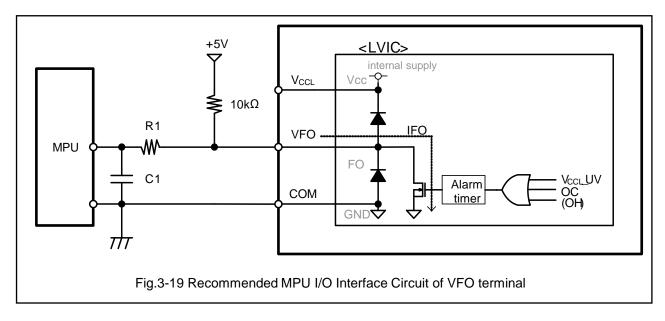

As shown in Fig.3-19, it is possible that the fault status output VFO terminal connects directly to the MPU. VFO terminal is open drain configured, thus this terminal should be pulled up by a resistor of approximate  $10k\Omega$  to the positive side of the 5V or 3.3V external logic power supply, which is the same as the input signals. It is also recommended that the by-pass capacitors C1 should be connected at the MPU, and the inrush current limitation resistance R1, which is more than  $5k\Omega$ , should be connected between the MPU and the VFO terminal. These signal lines should be wired as short as possible to each device.

Fault status output VFO function is activated by the UV of V<sub>CCL</sub>, OC and OH. (OH is applied to "6MBP15VSH060-50", "6MBP20VSC060-50" and "6MBP30VSC060-50".)

Fig.3-19 shows that the diodes in the IPM are electrically connected to the  $V_{CCL}$ , VFO and COM terminals. They should not be used for the voltage clamp intentionally to prevent major problems and destroy the IPM.

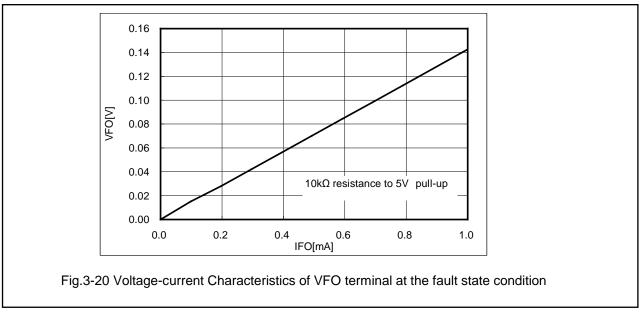

Fig.3-20 shows the Voltage-current characteristics of VFO terminal at fault state condition. The IFO is the sink current of the VFO terminal as shown in Fig.3-19.

# 7. Temperature Sensor Output Terminal TEMP

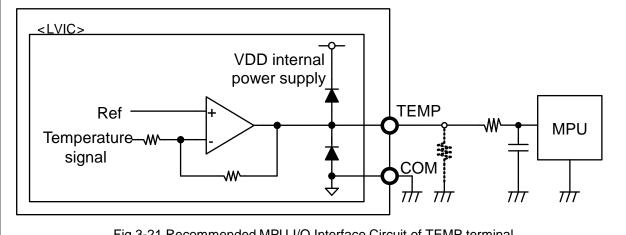

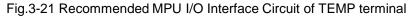

As shown in Fig. 3-21, the temperature sensor output TEMP can be connected to MPU directly.

It is recommended that a by-pass capacitor and >10k $\Omega$  of inrush current limiting resistor are connected between the TEMP terminal and the MPU. These signal lines should be wired as short as possible to each device.

The IPM has a built-in temperature sensor, and it can output an analog voltage according to the LVIC temperature. This function doesn't protect the IPM, and there is no fault signal output.

"6MBP15VSH060-50", "6MBP20VSC060-50" and "6MBP30VSC060-50" have a built-in over-heating protection. If the temperature exceeds TOH, these IPMs output a fault signal by the over-heating protection function.

A diode is electrically connected between TEMP and COM terminal as shown in Fig. 3-12. The purpose of the diode is a protection of the IPM from an input surge voltage. Don't use the diode as a voltage clamp circuit because the IPM might be damaged.

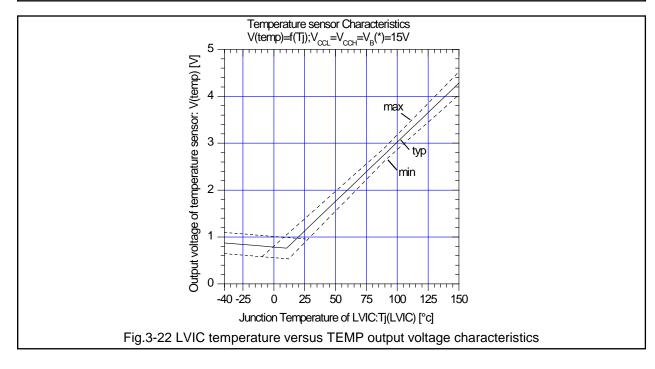

Fig.3-22 shows the LVIC temperature versus TEMP output voltage characteristics. It should be connected the TEMP terminal to a zener diode for the voltage clamp when the power supply of MPU is 3.3V.

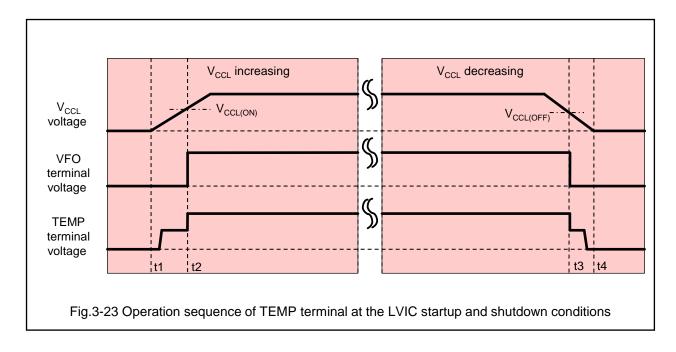

Fig.3-23 shows the operation sequence of TEMP terminal at the LVIC startup and shutdown conditions.

- t1-t2 : TEMP function is activated when  $V_{CCL}$  exceeds  $V_{CCL(ON)}$ . If  $V_{CCL}$  is less than  $V_{CCL(ON)}$ , the TEMP terminal voltage is the same as the clamp voltage.

- t2-t3 : TEMP terminal voltage rises to the voltage determined with LVIC temperature. In case the temperature is clamping operation, the TEMP terminal voltage is the same as the clamp voltage even though V<sub>CCL</sub> is less than V<sub>CCL(ON)</sub>.

- t3-t4 : TEMP function is reset when V<sub>CCL</sub> falls below V<sub>CCL(OFF)</sub>. TEMP terminal voltage becomes shutdown and the TEMP terminal voltage is the same as the clamp voltage.

## 8. Over Heating Protection

The over-heating protection (OH) functions is integrated into "6MBP15VSH060-50", "6MBP20VSC060-50" and "6MBP30VSC060-50".

The OH function monitors the LVIC junction temperature.

The TOH sensor position is shown in Fig.2-2.

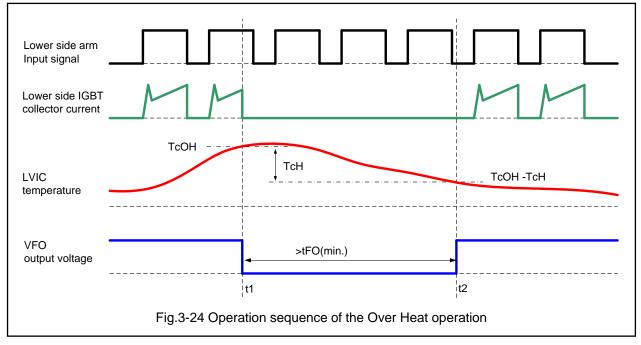

As shown in Fig.3-24, the IPM shutdown all lower side IGBTs while the LVIC temperature exceeds TOH. The fault status is reset when the LVIC temperature drops below (TOH-TOH(hys)).

- t1 : The fault status is activated and all IGBTs of the lower side arm shutdown, when LVIC temperature exceeds case overheating protection (OH) temperature TOH.

- t2 : The fault status, which outputs over  $t_{FO}$ , is reset and next input signal is activated, when LVIC temperature falls below TOH TOH(hys) which is the case overheating protection hysteresis.

## **Power Terminals**

| Contents                                                  | Page |

|-----------------------------------------------------------|------|

| 1. Connection of Bus Input terminal and Low Side Emitters | 4-2  |

| 2. Setting of Shunt Resister of Over Current Protection   | 4-3  |

### 1. Connection of bus input terminal and low side emitters

In this chapter, the guideline and precautions in circuit design on the power terminals, such as how to determine the resistance of shunt resister are explained.

#### (1) Description of the power terminals

Table 4-1 shows the detail about the power terminals.

#### Table 4-1 Detail description of power terminals

| Terminal Name  | Description                                                                                                                                                                                                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ρ              | Positive bus voltage input<br>It is internally connected to the collector of the high-side IGBTs.<br>In order to suppress the surge voltage caused by the wiring or PCB pattern<br>inductance of the bus voltage, connect a snubber capacitor close to this pin.<br>(Typically metal film capacitors are used) |

| U,V,W          | Motor output terminal<br>Inverter output terminals for connecting to motor load.                                                                                                                                                                                                                               |

| N(U),N(V),N(W) | Negative bus voltage input terminals<br>These terminals are connected to the low-side IGBT emitter of the each phase.<br>In order to observe the current on each phase, shunt resisters are inserted<br>between these terminals and the negative bus voltage input (power ground).                             |

#### (2) Recommended wiring of shunt resister and snubber capacitor

External current sensing resistors are applied to detect OC (over current) condition or phase currents. A long wiring patterns between the shunt resistor and the IPM will cause excessive surge that might damage internal IC, and current detection components. To decrease the pattern inductance, the wiring between the shunt resistors and the IPM should be as short as possible.

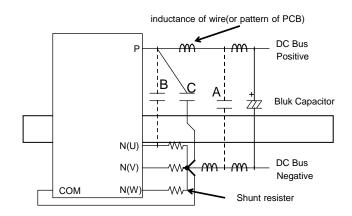

As shown in the Fig.4-1, snubber capacitors should be installed in the right location so as to suppress surge voltage effectively. Generally a 0.1 ~ 0.22  $\mu$ F snubber is recommended. If the snubber capacitor is installed in wrong location "A" as shown in the Fig.4-1, the snubber capacitor can not suppress the surge voltage effectively because inductance of wiring is not negligible.

If the capacitor is installed in the location "B", the charging and discharging currents generated by wiring and the snubber capacitor will appear on the shunt resistor. This will impact the current sensing signal and the OC protection level will be lower than the calculated design value. Although the suppression effect when the snubber capacitor is installed in location "B" is greater than the location "A" or "C", the location "C" is a reasonable position considering the impact to the current sensing accuracy. Therefore, the location "C" is generally used.

Fig.4-1 Recommended wiring of shunt resistor and snubber capacitor

### 2. Setting of Shunt Resister of Over Current Protection

#### (1) Selecting current sensing shunt resistor

The value of current sensing resistor is calculated by the following equation:

$$R_{Sh} = \frac{V_{IS(ref)}}{I_{OC}}$$

(4.1)

Where  $V_{IS(ref)}$  is the Over current protection (OC) reference voltage level of the IPM and I<sub>OC</sub> is the current of OC detection level.  $V_{IS(ref)}$  is 0.43V(min.), 0.48V(typ.) and 0.53V(max.). And R<sub>Sh</sub> is the Resistance of the shunt resister.

The maximum value of OC level should be set lower than the repetitive peak collector current in the spec sheet of this IPM considering the tolerance of shunt resistor.

For example, if OC level is set 30A, the recommended value of the shunt resistor is calculated as:

$$R_{Sh(\min)} = \frac{V_{IS(ref)(\max)}}{I_{\Omega C}} = \frac{0.53}{60} = 8.8 \,[\text{m}\Omega]$$

(4.2)

Where R<sub>Sh(min)</sub> is the minimum resistance of the shunt resister.

Based on above expressions, minimum shunt resistance of shunt resister is introduced.

It's note that a proper resistance should be chosen and confirmed considering OC level required in the practical application.

#### (2) Filter delay time setting of over current protection

An external RC filter is necessary in the over current sensing circuit to prevent malfunction of OC caused by noise. The RC time constant is determined depending on the applying time of noise and the short circuit withstand capability of IGBTs. It is recommended to be set approximately  $1.5\mu$ s.

When the voltage of the shunt resistor exceeds the OC level, the filter delay time (t<sub>delay</sub>) that the input voltage of IS terminal rises to the OC level is caused by RC filter delay time constant and it is given by:

$$t_{(delay)} = -\tau \cdot \ln(1 - \frac{V_{IS(ref)(max)}}{R_{Sh} \cdot I_P})$$

(4.3)

Where  $\tau$  is the RC time constant, I<sub>P</sub> is the peak current flowing through the shunt resister. In addition, there is the shutdown propagation delay t<sub>d(IS)</sub> of OC. Therefore, the total time t<sub>total</sub> from OC triggered to shutdown of the IGBT becomes:

$$t_{total} = t_{delay} + t_{d(IS)}$$

(4.4)

The total delay time t<sub>total</sub> must be considered the short circuit withstand capability of IGBT.

Please confirm a proper delay time in the actual equipment.

## **Recommended wiring and layout**

| Contents                                        | Page |

|-------------------------------------------------|------|

| 1. Examples of Application Circuits             | 5-2  |

| 2. Recommendation and Precautions in PCB design | 5-5  |

### 1. Examples of Application Circuits

In this chapter, a recommended wiring and layout are explained At first, hints and cautions in design are described with example of application circuit in section 1.

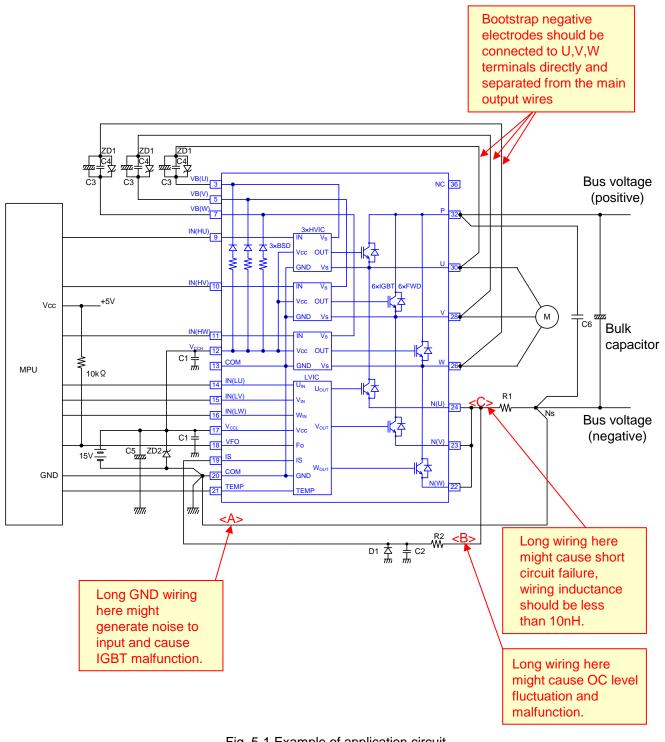

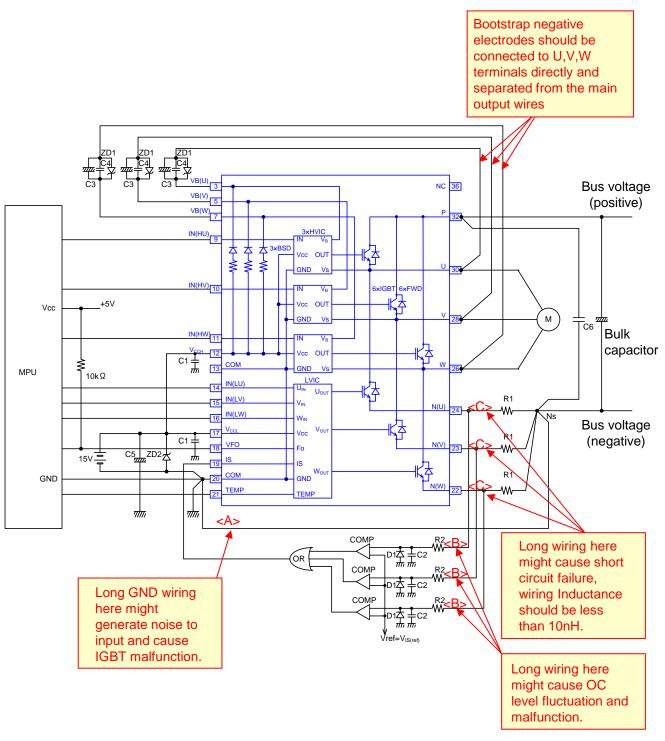

Fig. 5-1 and Fig.5-2 show examples of application circuit, and its Notes. In these figure, although two method of current sense are shown, these Notes are common.

Fig. 5-1 Example of application circuit (Sensing currents at once with 1 shunt resistor)

FC Fuji Electric Co., Ltd. MT6M10528 Rev.1.3 Jun.-2015

Fig. 5-2 Another example of application circuit (Sensing currents of each phase using external protection circuit)

F Fuji Electric Co., Ltd. MT6M10528 Rev.1.3 Jun.-2015

#### <Note>

- Input signal for IGBT driving is High-Active. The input circuit of the IC has a built-in pull-down

resistor. To prevent a malfunction, the wiring of each input should be as short as possible. When

using R-C coupling circuit, make sure the input signal level meet the turn-on and turn-off threshold

voltage.

- 2. The IPM has a built-in HVIC and it is possible to be connected to a microprocessor (MPU) directly without any photo-coupler or pulse-transformer isolation.

- 3. VFO output is open drain type. It should be pulled up to the positive side of a 5V power supply by a resistor of about  $10k\Omega$ .

- 4. To prevent erroneous protection, the wiring of (A), (B), (C) should be as short as possible.

- The time constant R2-C2 of the protection circuit should be selected approximately 1.5μs. Over current (OC) shutdown time might vary due to the wiring pattern. Tight tolerance, tempcompensated type is recommended for R2, C2.

- 6. Please recommended to set the threshold voltage of the comparator reference input to be same as the IPM OC trip reference voltage V<sub>IS(ref)</sub>.

- 7. Please use high speed type comparator and logic IC to detect OC condition quickly.

- 8. If negative voltage is applied to R1 during the switching operation, a schottky barrier diode D1 is recommended to be connected.

- 9. All capacitors should be connected as close to the terminals of the IPM as possible. (C1, C4 : narrow temperature drift, higher frequency and DC bias characteristic ceramic type are recommended, and C3, C5: narrow temperature drift, higher frequency and electrolytic type.)

- To prevent surge destruction, the wiring between the snubber capacitor and the P terminal, Ns node should be as short as possible. Generally 0.1μ to 0.22μF snubber capacitor (C6) between the P terminal and Ns node is recommended.

- 11. Two COM terminals (9 & 16 pin) are electrically connected inside the IPM, it must be connected either one to the signal GND outside and leave another one open.

- 12. It is recommended to insert a zener-diode (22V) between each pair of control supply terminals to prevent surge destruction.

- 13. If signal GND is connected to power GND by broad pattern, it may cause a malfunction by power GND fluctuation. It is recommended to connect signal GND and power GND at one point.

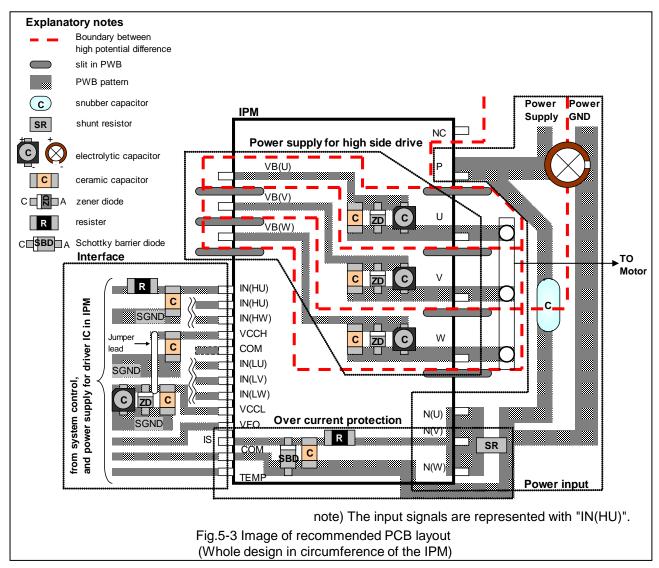

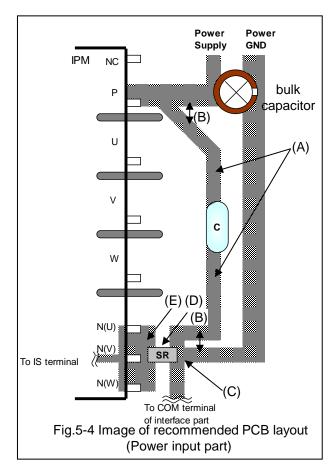

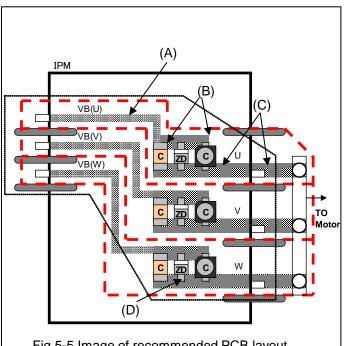

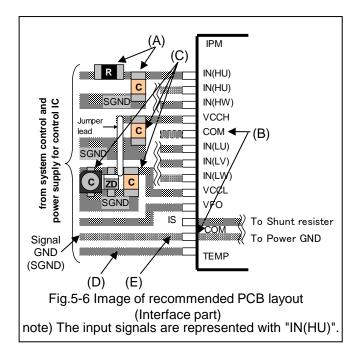

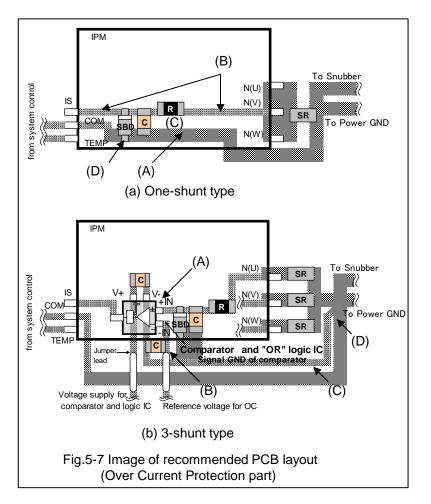

### 2. Recommendation and Precautions in PCB design

In this section, the recommended pattern layout and precautions in PCB design are described. Fig.5-3 to Fig.5-7 show the image of recommended PCB layout, referring Fig.5-1 and Fig.5-2. In these Fig., the input signals from system control are represented with "IN(HU)".

The recommendation and precautions are as follows,